## **NEC**

## **User's Manual**

# $\mu$ PD780058, 780058Y Subseries

## 8-Bit Single-Chip Microcontrollers

```

μPD780053

μPD780053Y

μPD780054

μPD780054Y

μPD780055

μPD780055Y

μPD780056

μPD780056Y

μPD780058

μPD780058BY

μPD780058B

μPD78F0058Y

μPD780053Y(A)

μPD78F0058

μPD780053(A)

μPD780054Y(A)

μPD780054(A)

μPD780055Y(A)

μPD780055(A)

μPD780056Y(A)

μPD780056(A)

μPD780058BY(A)

μPD780058B(A)

```

Document No. U12013EJ3V2UD00 (3rd edition) Date Published February 2003 N CP (K)

© NEC Electronics Corporation 1997, 2003 Printed in Japan [MEMO]

ww.DataSheet4U.cor

#### NOTES FOR CMOS DEVICES -

#### 1 PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

ww.DataSheet4U.con

#### ② HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### (3) STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

FIP, EEPROM, and IEBus are trademarks of NEC Electronics Corporation.

Windows and Windows NT are either registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries.

PC/AT is a trademark of International Business Machines Corporation.

HP9000 Series 700 and HP-UX are trademarks of Hewlett-Packard Company.

SPARCstation is a trademark of SPARC International, Inc.

SunOS is a trademark of Sun Microsystems, Inc.

TRON stands for The Realtime Operating system Nucleus.

ITRON is an abbreviation of Industrial TRON.

These commodities, technology or software, must be exported in accordance with the export administration regulations of the exporting country. Diversion contrary to the law of that country is prohibited.

Purchase of NEC Electronics I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

- The information in this document is current as of January, 2003. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual

property rights of third parties by or arising from the use of NEC Electronics products listed in this document

or any other liability arising from the use of such products. No license, express, implied or otherwise, is

granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these

circuits, software and information in the design of a customer's equipment shall be done under the full

responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by

customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

- The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

#### (Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

## **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC Electronics product in your application, please contact the NEC Electronics office in your country to obtain a list of authorized representatives and distributors. They will verify:

- Device availability

- Ordering information

- · Product release schedule

- www.DataSheet4U.com Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### NEC Electronics America, Inc. (U.S.) • Filiale Italiana

Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### **NEC Electronics (Europe) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 01 Fax: 0211-65 03 327

#### • Sucursal en España

Madrid, Spain Tel: 091-504 27 87 Fax: 091-504 28 60

#### Succursale Française

Vélizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

#### Branch The Netherlands

Eindhoven, The Netherlands Tel: 040-244 58 45 Fax: 040-244 45 80

#### Tyskland Filial

Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388

### United Kingdom Branch

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

#### **NEC Electronics Hong Kong Ltd.**

Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

#### **NEC Electronics Hong Kong Ltd.**

Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

#### NEC Electronics Shanghai, Ltd.

Shanghai, P.R. China Tel: 021-6841-1138 Fax: 021-6841-1137

#### **NEC Electronics Taiwan Ltd.**

Taipei. Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

#### **NEC Electronics Singapore Pte. Ltd.**

Novena Square, Singapore

Tel: 6253-8311 Fax: 6250-3583

## Major Revisions in This Edition (1/2)

| Page               | Description                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Throughout         | Deletion of following product • μPD780058Y                                                                                                                                                                                                                                                                                                                                               |

|                    | Addition of following products<br>• $\mu$ PD780058B, 780058BY, 780053(A), 780053Y(A), 780054(A), 780054Y(A), 780055(A), 780055Y(A), 780056Y(A), 780058B(A), 780058BY(A)                                                                                                                                                                                                                  |

|                    | Deletion of following packages  • 80-pin plastic QFP (GC-3B9 type)  • 80-pin plastic TQFP (GK-BE9 type)                                                                                                                                                                                                                                                                                  |

| i4U.com            | Addition of following package  • 80-pin plastic TQFP (GK-9EU type)                                                                                                                                                                                                                                                                                                                       |

| pp. 31, 32, 38, 39 | <ul> <li>1.1 Features, 1.7 Outline of Functions</li> <li>Change of operating voltage range of A/D and D/A converters of μPD780058 and 78F0058</li> <li>Change of supply voltage of μPD78F0058</li> </ul>                                                                                                                                                                                 |

| p. 40              | Addition of 1.9 Differences Between Standard Model and (A) Model                                                                                                                                                                                                                                                                                                                         |

| pp. 41, 42, 48, 49 | <ul> <li>2.1 Features, 2.7 Outline of Functions</li> <li>Change of operating voltage range of A/D and D/A converters of μPD78F0058Y</li> <li>Change of supply voltage of μPD78F0058Y</li> </ul>                                                                                                                                                                                          |

| p. 50              | Addition of 2.9 Differences Between Standard Model and (A) Model                                                                                                                                                                                                                                                                                                                         |

| p. 60              | Change of processing when A/D converter is not used in 3.2.11 AVREF0                                                                                                                                                                                                                                                                                                                     |

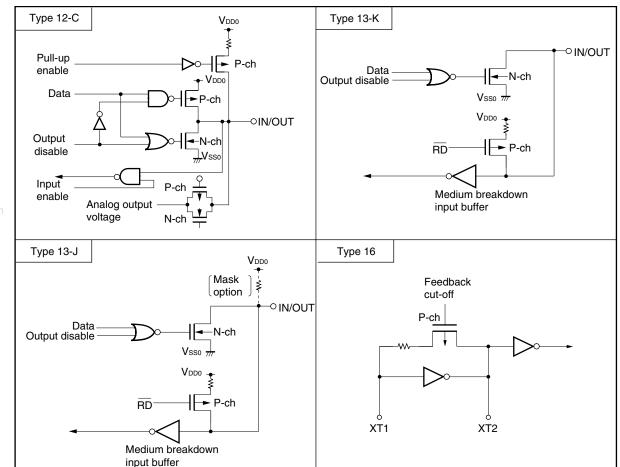

| pp. 62, 63         | Change of recommended connection of unused pins and connection of P60 to P63, AVREF1, and VPP pins in <b>Table 3-1 Pin I/O Circuit Types</b>                                                                                                                                                                                                                                             |

| p. 75              | Change of processing when A/D converter is not used in 4.2.11 AVREF0                                                                                                                                                                                                                                                                                                                     |

| pp. 77, 78         | Change of recommended connection of unused pins and connection of P60 to P63, AVREF1, and VPP pins in <b>Table 4-1 Pin I/O Circuit Types</b>                                                                                                                                                                                                                                             |

| p. 132             | Modification of Note 2 in 6.2.8 Port 6                                                                                                                                                                                                                                                                                                                                                   |

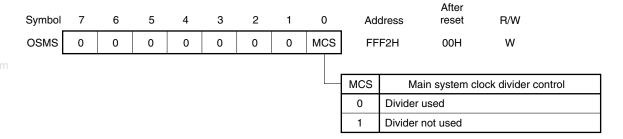

| p. 149             | Addition of note on feedback resistor to Figure 7-3 Processor Clock Control Register Format                                                                                                                                                                                                                                                                                              |

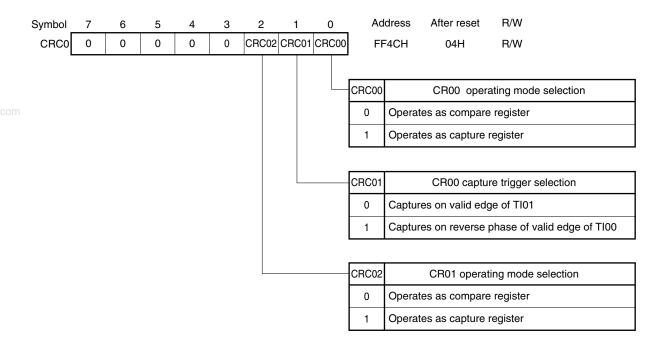

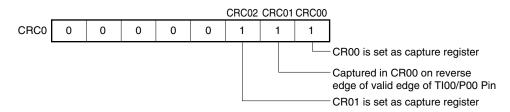

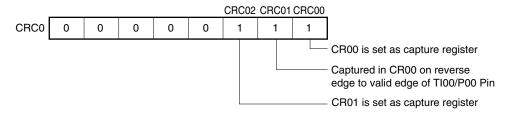

| p. 167             | Addition of Table 8-5 INTP1/TI01 Pin Valid Edge and CR00 Capture Trigger Valid Edge                                                                                                                                                                                                                                                                                                      |

| p. 168             | Addition of Table 8-6 INTP0/TI00 Pin Valid Edge and CR01 Capture Trigger Valid Edge                                                                                                                                                                                                                                                                                                      |

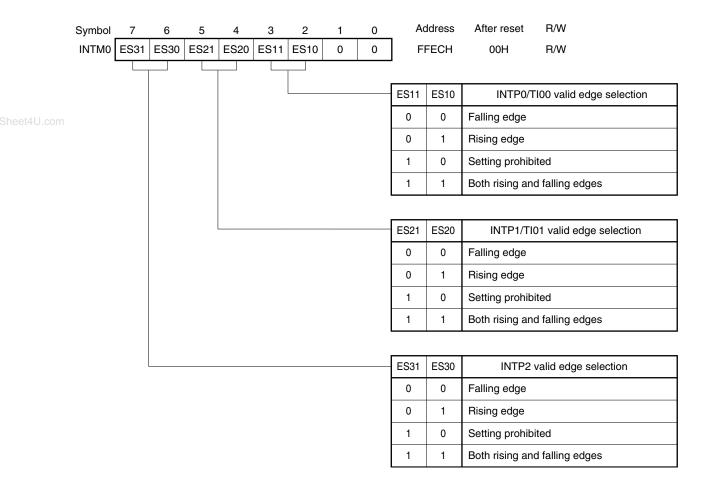

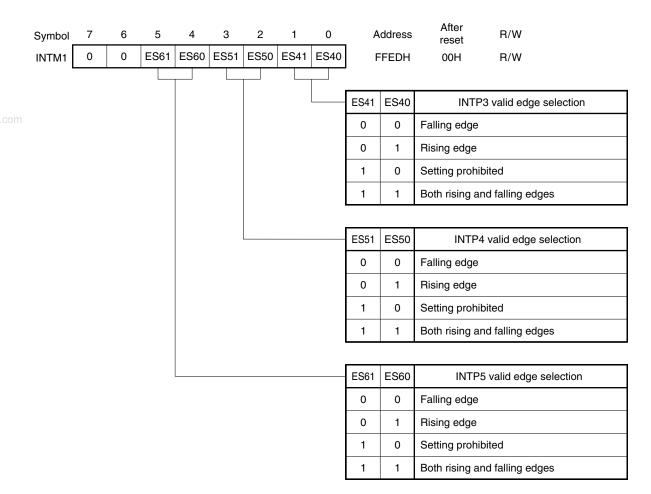

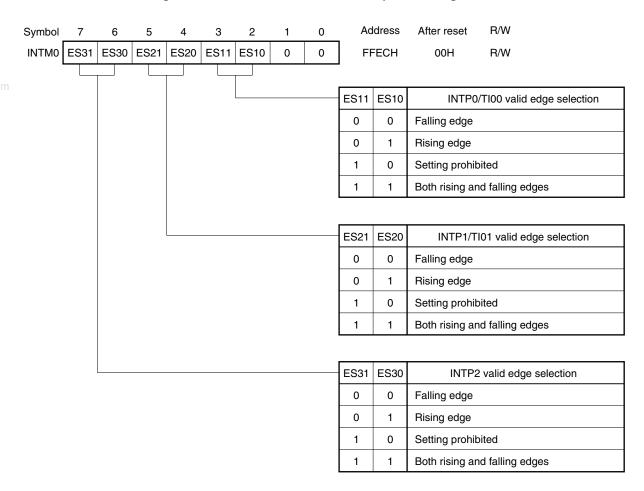

| p. 177             | Correction of note on valid edge of INTP0/TI00/P00 and INTP1/TI01/P01 pin in Figure 8-8 Format of External Interrupt Mode Register 0                                                                                                                                                                                                                                                     |

| p. 185             | Addition of Figure 8-17 Configuration of PPG Output Addition of Figure 8-18 PPG Output Operation Timing                                                                                                                                                                                                                                                                                  |

| pp. 201 to 204     | 8.5 16-Bit Timer/Event Counter Operating Cautions  Addition of description on TI01/P01/INTP1 to (5) Valid edge setting  Addition of (c) One-shot pulse output function to (6) Re-trigger of one-shot pulse  Addition of (8) Conflict operation  Addition of (9) Timer operation  Addition of (10) Capture operation  Addition of (11) Compare operation  Addition of (12) Edge detection |

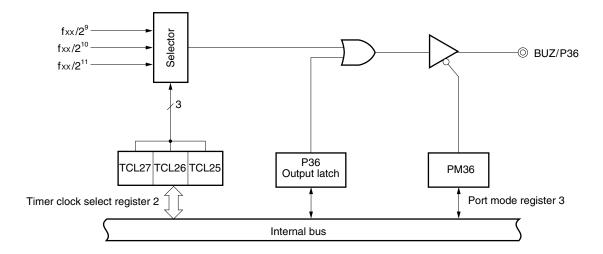

| p. 235             | Modification of note on changing count clock in Figure 10-2 Timer Clock Select Register 2 Format                                                                                                                                                                                                                                                                                         |

| p. 242             | Modification of note on changing count clock in Figure 11-2 Timer Clock Select Register 2 Format                                                                                                                                                                                                                                                                                         |

| p. 252             | Addition of note on rewriting TCL2 in Figure 13-2 Format of Timer Clock Select Register 2                                                                                                                                                                                                                                                                                                |

## **Major Revisions in This Edition (2/2)**

| Page                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

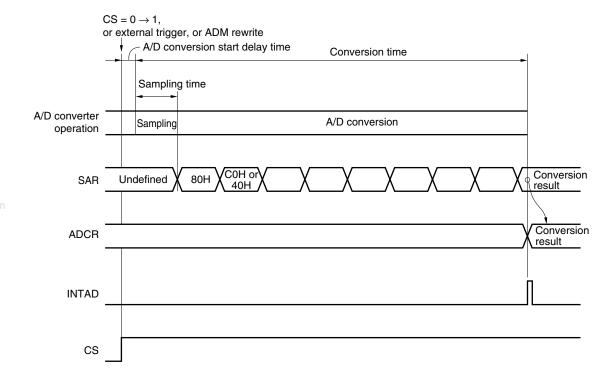

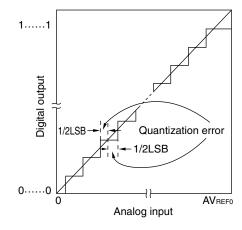

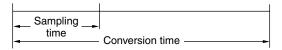

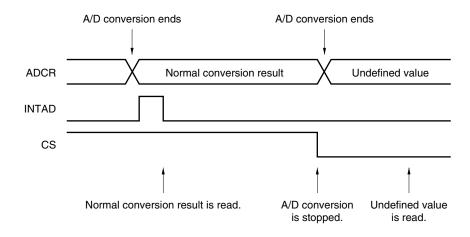

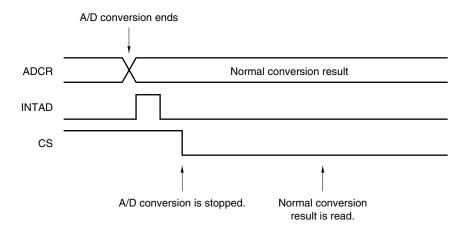

| p. 263                 | Modification of Figure 14-5 A/D Converter Basic Operation Addition of Table 14-2 A/D Conversion Sampling Time and A/D Converter Start Delay Time                                                                                                                                                                                                                                                                                     |

| pp. 267, 268           | Addition of 14.5 How to Read A/D Converter Characteristics Table                                                                                                                                                                                                                                                                                                                                                                     |

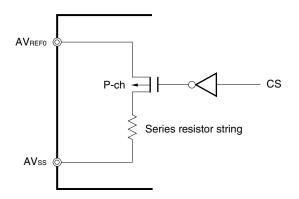

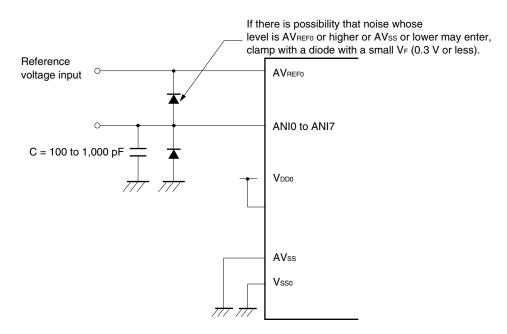

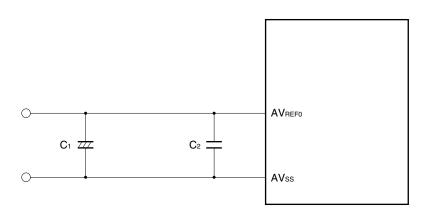

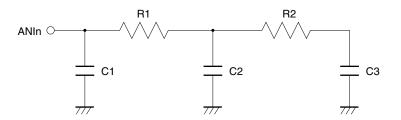

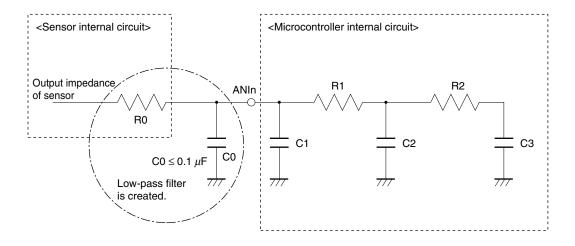

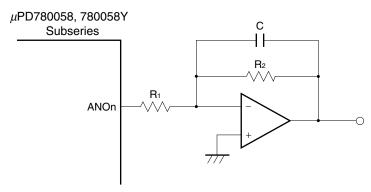

| pp. 269, 270, 272, 273 | 14.6 A/D Converter Cautions Change of description in (1) Power consumption in standby mode Addition of (3) Conflict operations Addition of (6) Input impedance of ANI0 to ANI7 pins Addition of (10) Timing at which A/D conversion result is undefined Addition of (11) Notes on board design Addition of (12) AVREFO pin Addition of (13) Internal equivalent circuit of ANI0 to ANI7 pins and permissible signal source impedance |

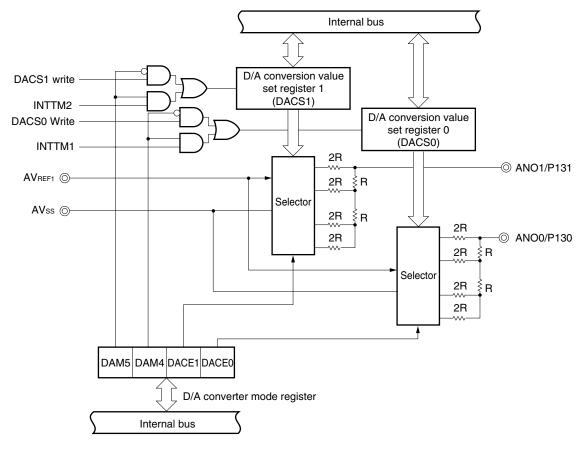

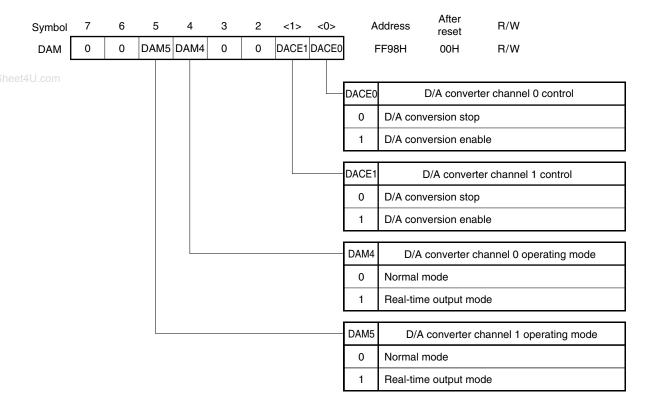

| p. 280                 | Addition of description of processing when D/A converter is not used in 15.5 D/A Converter Cautions (3) AVREF1 pin                                                                                                                                                                                                                                                                                                                   |

| p. 379                 | Addition of 17.4.7 Restrictions in I <sup>2</sup> C bus mode 2                                                                                                                                                                                                                                                                                                                                                                       |

| p. 468                 | Addition of 19.4.5 Restrictions in UART mode 2                                                                                                                                                                                                                                                                                                                                                                                       |

| p. 477                 | Addition of Caution when interrupt is acknowledged to Figure 21-2 Interrupt Request Flag Register Format                                                                                                                                                                                                                                                                                                                             |

| p. 483                 | Addition of description on TI01/P01/INTP1 pin to Figure 21-5 Format of External Interrupt  Mode Register 0                                                                                                                                                                                                                                                                                                                           |

| p. 525                 | Addition of Caution to 25.1 ROM Correction Function                                                                                                                                                                                                                                                                                                                                                                                  |

| p. 535                 | Modification of Table 26-1 Differences Between $\mu$ PD78F0058, 78F0058Y and Mask ROM Versions                                                                                                                                                                                                                                                                                                                                       |

| pp. 538 to 549         | Total revision of description on flash memory programming as 26.3 Flash Memory Characteristics                                                                                                                                                                                                                                                                                                                                       |

| pp. 567 to 596         | Addition of CHAPTER 28 ELECTRICAL SPECIFICATIONS (MASK ROM VERSION)                                                                                                                                                                                                                                                                                                                                                                  |

| pp. 597 to 626         | Addition of CHAPTER 29 ELECTRICAL SPECIFICATIONS (FLASH MEMORY VERSION)                                                                                                                                                                                                                                                                                                                                                              |

| pp. 627 to 657         | Addition of CHAPTER 30 ELECTRICAL SPECIFICATIONS (FLASH MEMORY VERSION (VDD = 2.2 V))                                                                                                                                                                                                                                                                                                                                                |

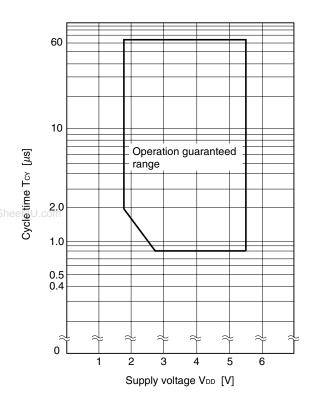

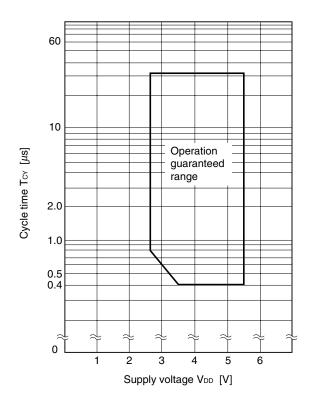

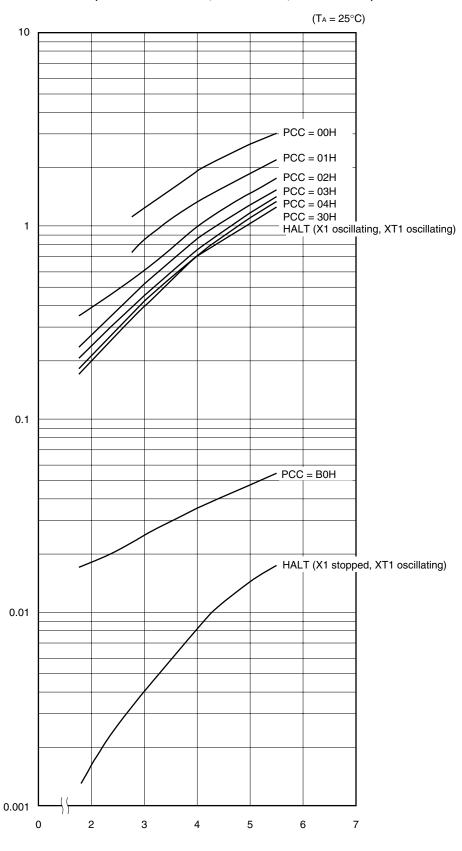

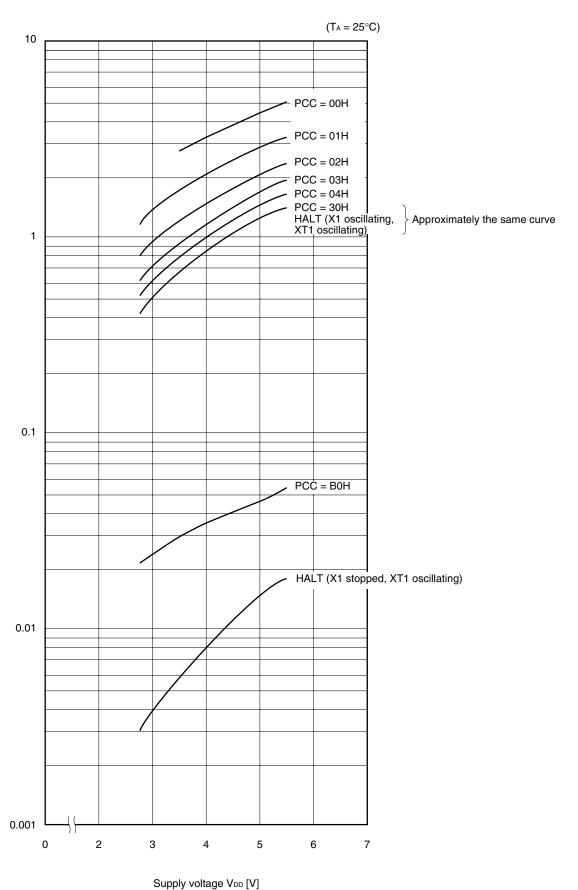

| pp. 658, 659           | Addition of CHAPTER 31 CHARACTERISTICS CURVES (REFERENCE VALUES)                                                                                                                                                                                                                                                                                                                                                                     |

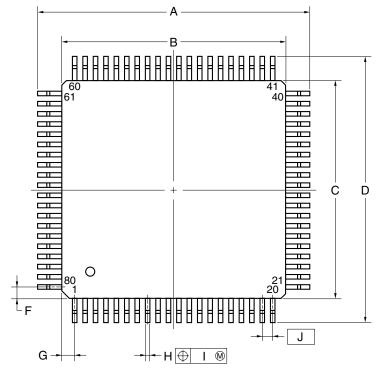

| pp. 660, 661           | Addition of CHAPTER 32 PACKAGE DRAWINGS                                                                                                                                                                                                                                                                                                                                                                                              |

| pp. 662 to 665         | Addition of CHAPTER 33 RECOMMENDED SOLDERING CONDITIONS                                                                                                                                                                                                                                                                                                                                                                              |

| pp. 666, 667           | Correction of APPENDIX A DIFFERENCES BETWEEN $\mu$ PD78054, 78058F, AND 780058 SUBSERIES                                                                                                                                                                                                                                                                                                                                             |

| pp. 668 to 684         | Total revision of APPENDIX B DEVELOPMENT TOOLS  Transfer of description of embedded software to APPENDIX B DEVELOPMENT TOOLS                                                                                                                                                                                                                                                                                                         |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                      |

The mark ★ shows major revised points.

#### **PREFACE**

#### Readers

This manual has been prepared for user engineers who wish to understand the functions of the  $\mu$ PD780058 and 780058Y Subseries and design and develop its application systems and programs.

This manual is intended for the products in the following subseries.

- $\mu$ PD780058 Subseries  $\mu$ PD780053, 780054, 780055, 780056, 780058, 780058B, 78F0058, 780053(A), 780054(A), 780055(A), 780056(A), 780058B(A)

- μPD780058Y Subseries

μPD780053Y, 780054Y, 780055Y, 780056Y, 780058BY, 78F0058Y, 780053Y(A),

780054Y(A), 780055Y(A), 780056Y(A), 780058BY(A)

These products are collectively referred to as the " $\mu$ PD780058, 780058Y Subseries" in this manual.

**Purpose**

This manual is intended to give users an understanding of the functions described in the organization below.

Organization

The  $\mu$ PD780058, 780058Y Subseries manual is separated into two parts: this manual and the instruction edition (common to the 78K/0 Series).

μPD780058, 780058Y Subseries User's Manual (This manual)

- Pin functions

- Internal block functions

- Interrupts

- Other on-chip peripheral functions

- Electrical specifications

78K/0 Series User's Manual Instructions

- CPU functions

- Instruction set

- Explanation of each instruction

#### How to Read This Manual

It is assumed that readers of this manual have general knowledge of electrical engineering, logic circuits, and microcontrollers.

- O When using this manual as the manual for the  $\mu$ PD780053(A), 780054(A), 780055(A), 780056(A), 780058B(A), 780053Y(A), 780054Y(A), 780055Y(A), 780056Y(A), and 780058BY(A),

- → The only difference between these products and the μPD780053, 780054, 780055, 780056, 780058B, 780053Y, 780054Y, 780055Y, 780056Y, and 780058BY is the quality grade (see 1.9 Differences Between Standard Model and (A) Model, and 2.9 Differences Between Standard Model and (A) Model). The correspondence between the standard model and (A) model is as follows in CHAPTER 6 PORT FUNCTIONS to CHAPTER 27 INSTRUCTION SET OUTLINE.

```

\begin{array}{lll} \mu \text{PD780053} \to \mu \text{PD780053(A)} & \mu \text{PD780053Y} \to \mu \text{PD780053Y(A)} \\ \mu \text{PD780054} \to \mu \text{PD780054(A)} & \mu \text{PD780054Y} \to \mu \text{PD780054Y(A)} \\ \mu \text{PD780055} \to \mu \text{PD780055(A)} & \mu \text{PD780055Y} \to \mu \text{PD780055Y(A)} \\ \mu \text{PD780056} \to \mu \text{PD780056(A)} & \mu \text{PD780056Y} \to \mu \text{PD780056Y(A)} \\ \mu \text{PD780058B} \to \mu \text{PD780058B(A)} & \mu \text{PD780058BY} \to \mu \text{PD780058BY(A)} \end{array}

```

- O To gain a general understanding the functions:

- → Read this manual in the order of the contents.

- $\odot$  To know the  $\mu$ PD780058 and 780058Y Subseries instruction functions in detail:

- → Refer to the 78K/0 Series Instructions User's Manual (U12326E)

- How to interpret the register format:

- → For a bit number enclosed in angle brackets (<>), the bit name is defined as a reserved word in the RA78K0, and defined in the header file named sfrbit.h in the CC78K0.

- O To learn the function of a register whose register name is known:

- → Refer to APPENDIX C REGISTER INDEX.

- $\odot$  To see application examples of each function of the  $\mu$ PD780058, 780058Y Subseries:

- → Refer to 78K/0 Series Basics (III) Application Note (U10182E) separately available.

- $\odot$  To understand the electrical specifications of the  $\mu$ PD780058, 780058Y Subseries:

- ightarrow See Chapter 28 Electrical Specifications (Mask Rom Version), Chapter 29 Electrical Specifications (Flash Memory Version), Chapter 30 Electrical Specifications (Flash Memory Version (VDD = 2.2 V)).

- Caution Examples in this manual employ the "standard" quality grade for general electronics. When using examples in this manual for the "special" quality grade, review the quality grade of each part and/or circuit actually used.

www.DataSheet4U.co

**Chapter Organization**: This manual divides the descriptions for the  $\mu$ PD780058 and 780058Y Subseries into different chapters as shown below. Read only the chapters related to the device being used.

| Chapter                                                                   | μPD780058<br>Subseries | μPD780058Y<br>Subseries |

|---------------------------------------------------------------------------|------------------------|-------------------------|

| CHAPTER 1 Outline (μPD780058 Subseries)                                   | V                      | _                       |

| CHAPTER 2 Outline (µPD780058Y Subseries)                                  | _                      | √                       |

| CHAPTER 3 Pin Functions (µPD780058 Subseries)                             | $\sqrt{}$              | _                       |

| CHAPTER 4 Pin Functions (µPD780058Y Subseries)                            | _                      | √                       |

| CHAPTER 5 CPU Architecture                                                | √                      | √                       |

| CHAPTER 6 Port Functions                                                  | √                      | √                       |

| CHAPTER 7 Clock Generator                                                 | $\checkmark$           | √                       |

| CHAPTER 8 16-Bit Timer/Event Counter                                      | √                      | √                       |

| CHAPTER 9 8-Bit Timer/Event Counter                                       | $\checkmark$           | √                       |

| CHAPTER 10 Watch Timer                                                    | $\checkmark$           | √                       |

| CHAPTER 11 Watchdog Timer                                                 | $\sqrt{}$              | √                       |

| CHAPTER 12 Clock Output Controller                                        | $\checkmark$           | √                       |

| CHAPTER 13 Buzzer Output Controller                                       | $\sqrt{}$              | √                       |

| CHAPTER 14 A/D Converter                                                  | $\sqrt{}$              | √                       |

| CHAPTER 15 D/A Converter                                                  | $\sqrt{}$              | √                       |

| CHAPTER 16 Serial Interface Channel 0 (µPD780058 Subseries)               | $\sqrt{}$              | _                       |

| CHAPTER 17 Serial Interface Channel 0 (µPD780058Y Subseries)              | _                      | √                       |

| CHAPTER 18 Serial Interface Channel 1                                     | $\sqrt{}$              | √                       |

| CHAPTER 19 Serial Interface Channel 2                                     | $\sqrt{}$              | √                       |

| CHAPTER 20 Real-Time Output Port                                          | √                      | √                       |

| CHAPTER 21 Interrupt and Test Functions                                   | √                      | √                       |

| CHAPTER 22 External Device Expansion Function                             | $\sqrt{}$              | √                       |

| CHAPTER 23 Standby Function                                               | $\sqrt{}$              | √                       |

| CHAPTER 24 Reset Function                                                 | $\sqrt{}$              | √                       |

| CHAPTER 25 ROM Correction                                                 | $\sqrt{}$              | √                       |

| CHAPTER 26 μPD78F0058, μPD78F0058Y                                        | $\sqrt{}$              | √                       |

| CHAPTER 27 Outline of Instruction Set                                     | √                      | √                       |

| CHAPTER 28 ELECTRICAL SPECIFICATIONS (MASK ROM VERSION)                   | √                      | √                       |

| CHAPTER 29 ELECTRICAL SPECIFICATIONS (FLASH MEMORY VERSION)               | √                      | √                       |

| CHAPTER 30 ELECTRICAL SPECIFICATIONS (FLASH MEMORY VERSION (VDD = 2.2 V)) | √                      | √                       |

| CHAPTER 31 CHARACTERISTICS CURVES (REFERENCE VALUES)                      | √                      | √                       |

| CHAPTER 32 PACKAGE DRAWINGS                                               | √                      | √                       |

| CHAPTER 33 RECOMMENDED SOLDERING CONDITIONS                               | √                      | √                       |

#### Differences Between $\mu$ PD780058 and $\mu$ PD780058Y Subseries:

The  $\mu$ PD780058 and  $\mu$ PD780058Y Subseries differ in the following functions of serial interface channel 0.

| Modes of serial interface channel 0  | μPD780058<br>Subseries | μPD780058Y<br>Subseries |

|--------------------------------------|------------------------|-------------------------|

| 3-wire serial I/O mode               | √                      | √                       |

| 2-wire serial I/O mode               | √                      | √                       |

| SBI (serial bus interface) mode      | V                      | _                       |

| I <sup>2</sup> C (inter IC) bus mode | _                      | V                       |

$\sqrt{\cdot}$  Supported

—: Not supported

**Legend** Data significance: Higher digits on the left and lower digits on the right

Active low representations:  $\overline{\times\!\times\!\times}$  (overscore over pin or signal name)

Note: Footnote for item marked with Note in the text.

Caution: Information requiring particular attention

**Remark**: Supplementary information Numeral representations: Binary ... ×××× or ××××B

Decimal ... xxxx

Hexadecimal ... xxxxH

versions. However, preliminary versions are not marked as such.

#### **★** Documents Related to Devices

| Document Name                              | Document No. |

|--------------------------------------------|--------------|

| μPD780058, 780058Y Subseries User's Manual | This manual  |

| 78K/0 Series Instruction User's Manual     | U12326E      |

| 78K/0 Series Basics (III) Application Note | U10182E      |

Caution The related documents listed above are subject to change without notice. Be sure to use the latest version of each document for designing.

#### **★** Documents Related to Software Development Tools (User's Manuals)

| Document Name                                       |                                                 | Document No. |

|-----------------------------------------------------|-------------------------------------------------|--------------|

| RA78K0 Assember Package                             | Operation                                       | U14445E      |

|                                                     | Language                                        | U14446E      |

|                                                     | Structure Assembly Language                     | U11789E      |

| CC78K0 C Compiler                                   | Operation                                       | U14297E      |

|                                                     | Language                                        | U14298E      |

| SM78K Series System Simulator Ver. 2.30 or Later    | Operation (Windows™ Based)                      | U15373E      |

|                                                     | External Part User Open Interface Specification | U15802E      |

| ID78K Series Integrated Debugger Ver. 2.30 or Later | Operation (Windows Based)                       | U15185E      |

| ARX78K0 Real-Time OS                                | Fundamentals                                    | U11537E      |

|                                                     | Installation                                    | U11536E      |

| Project Manager Ver. 3.12 or Later (Windows Based)  |                                                 | U14610E      |

#### **Documents Related to Hardware Development Tools (User's Manuals)**

| Document Name                    | Document No. |

|----------------------------------|--------------|

| IE-78K0-NS In-Circuit Emulator   | U13731E      |

| IE-78K0-NS-A In-Circuit Emulator | U14889E      |

| IE-780308-NS-EM1 Emulation Board | U13304E      |

| IE-78001-R-A In-Circuit Emulator | U14142E      |

| IE-780308-R-EM Emulation Board   | U11362E      |

### **Documents Related to Flash Memory Writing**

| Document Name                                | Document No. |

|----------------------------------------------|--------------|

| PG-FP3 Flash Memory Programmer User's Manual |              |

| PG-FP4 Flash Memory Programmer User's Manual | U15260E      |

#### **Other Related Documents**

|   | Document Name                                                                      | Document No. |

|---|------------------------------------------------------------------------------------|--------------|

| * | SEMICONDUCTOR SELECTION GUIDE - Products and Packages -                            | X13769X      |

| * | Semiconductor Device Mounting Technology Manual                                    | C10535E      |

|   | Quality Grades on NEC Semiconductor Devices                                        | C11531E      |

|   | NEC Semiconductor Device Reliability/Quality Control System                        | C10983E      |

|   | Guide to Prevent Damage for Semiconductor Devices by Electrostatic Discharge (ESD) | C11892E      |

Caution The related documents listed above are subject to change without notice. Be sure to use the latest version of each document for designing.

#### **CONTENTS**

|              | CHAPTE | ER 1 OUTLINE (μPD780058 SUBSERIES)                      | 31              |

|--------------|--------|---------------------------------------------------------|-----------------|

|              | 1.1    | Features                                                | 31              |

|              | 1.2    | Applications                                            | 32              |

|              | 1.3    | Ordering Information                                    | 32              |

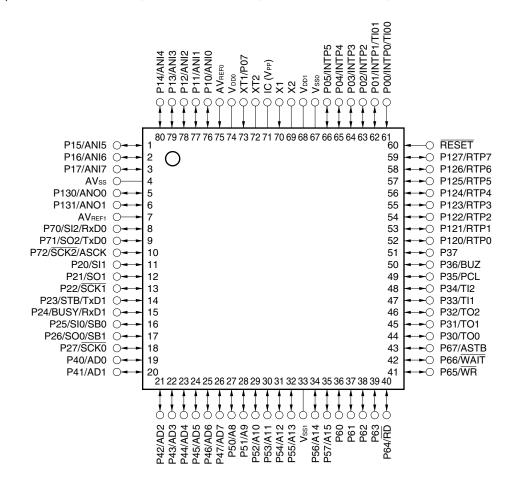

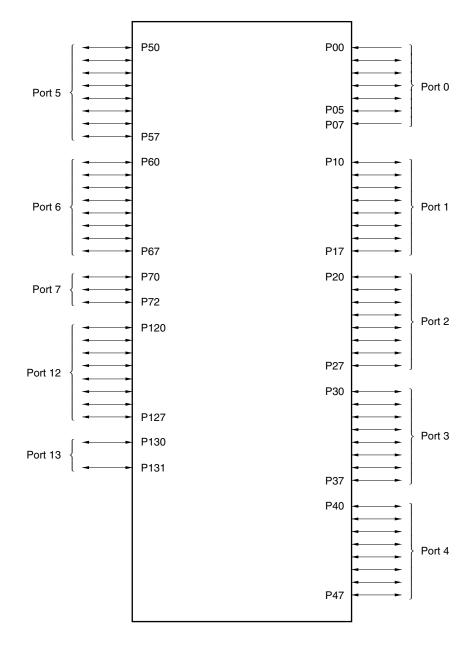

|              | 1.4    | Pin Configuration (Top View)                            | 33              |

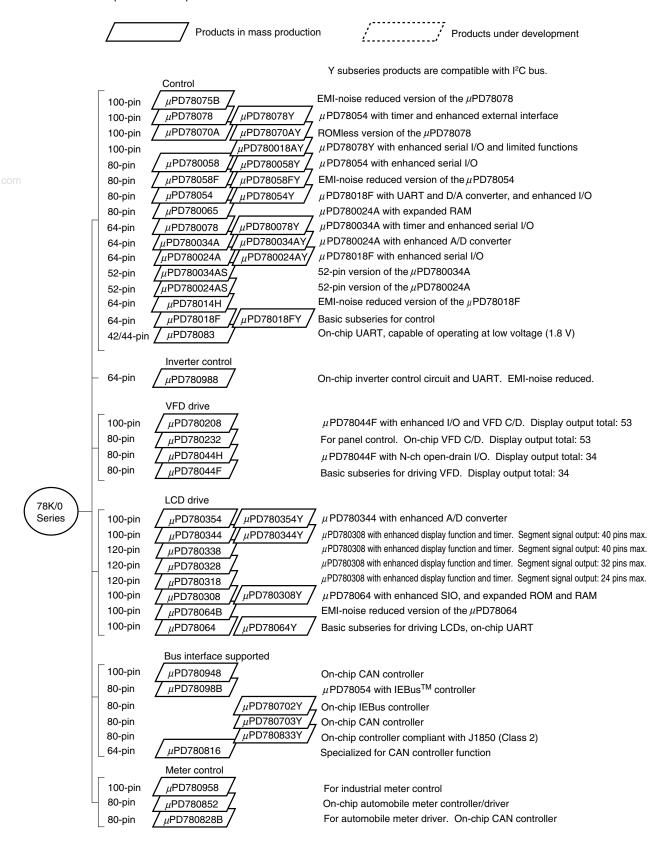

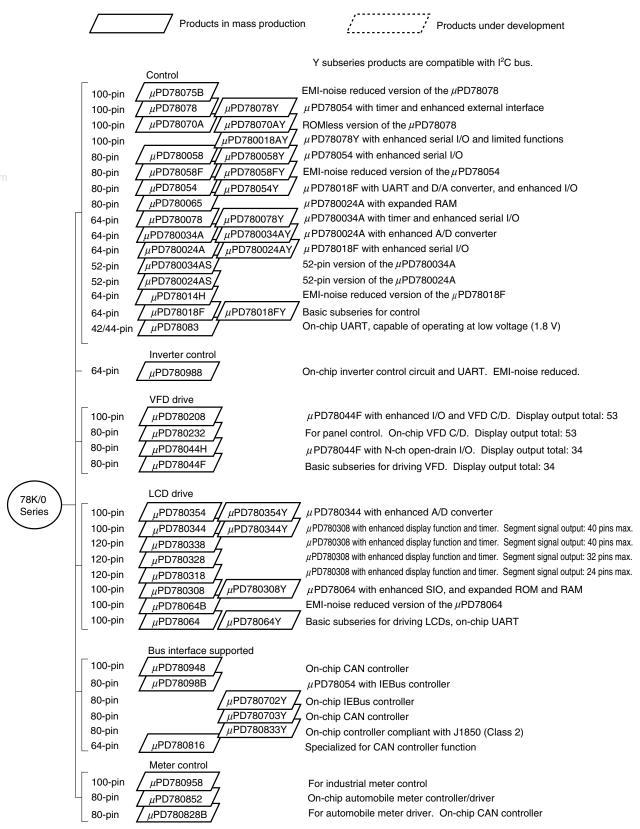

|              | 1.5    | 78K/0 Series Lineup                                     | 35              |

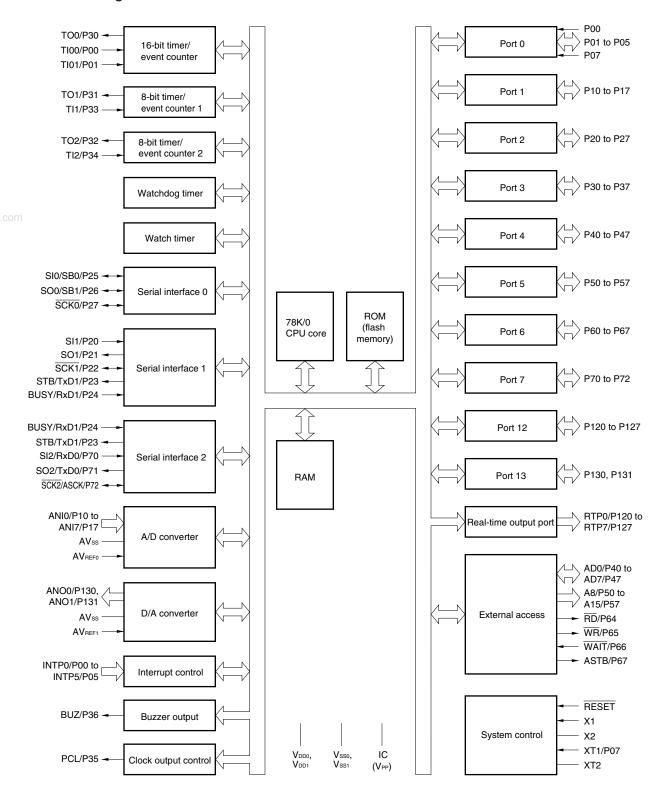

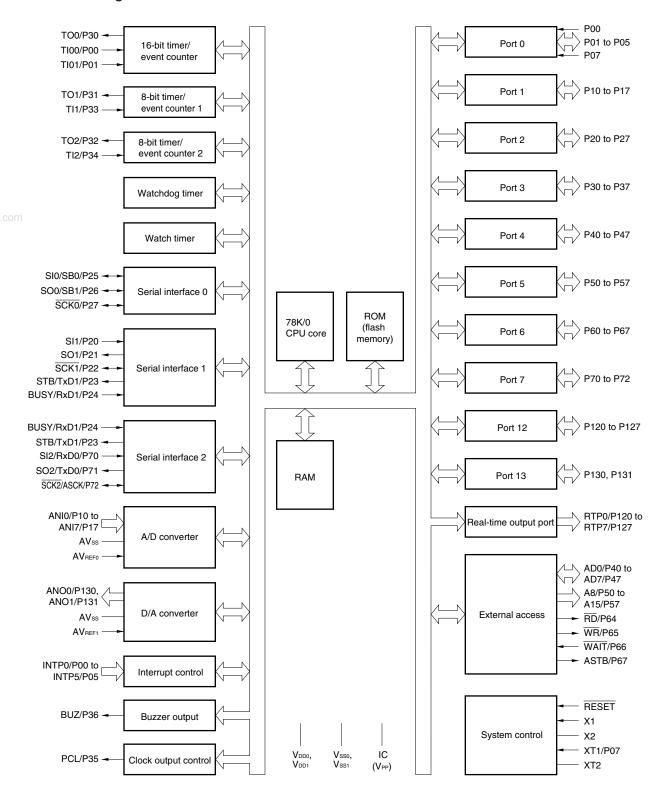

|              | 1.6    | Block Diagram                                           | 37              |

|              | 1.7    | Outline of Function                                     | 38              |

|              | 1.8    | Mask Options                                            | 40              |

| aSheet4U.con | 1.9    | Differences Between Standard Model and (A) Model        | 40              |

|              | CHAPTE | ER 2 OUTLINE (μPD780058Y SUBSERIES)                     | 41              |

|              |        | Features                                                | 41              |

|              | 2.2    | Applications                                            | 42              |

|              | 2.3    | Ordering Information                                    | 42              |

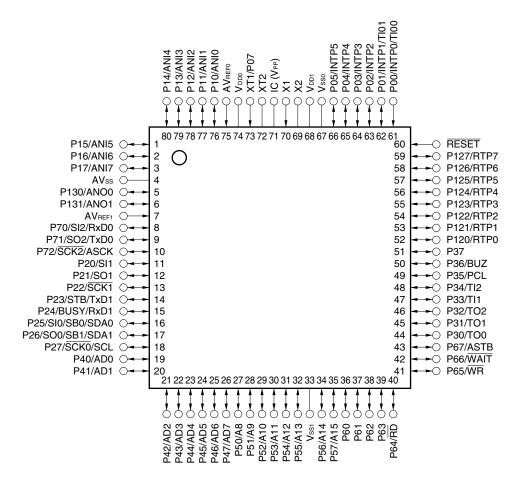

|              | 2.4    | Pin Configuration (Top View)                            | 43              |

|              |        | 78K/0 Series Lineup                                     | 45              |

|              | 2.6    | Block Diagram                                           | 47              |

|              | 2.7    | Outline of Functions                                    | 48              |

|              | 2.8    | Mask Options                                            | 50              |

| *            | 2.9    | Differences Between Standard Model and (A) Model        | 50              |

|              | CHADTE | ER 3 PIN FUNCTIONS (μPD780058 SUBSERIES)                | 51              |

|              |        | Pin Function List                                       | 51              |

|              |        | Description of Pin Functions                            | 55              |

|              | 3.2    | 3.2.1 P00 to P05, P07 (Port 0)                          | 55              |

|              |        | 3.2.2 P10 to P17 (Port 1)                               | 55              |

|              |        | 3.2.3 P20 to P27 (Port 2)                               | 56              |

|              |        | 3.2.4 P30 to P37 (Port 3)                               | 57              |

|              |        | 3.2.5 P40 to P47 (Port 4)                               | 57              |

|              |        | 3.2.6 P50 to P57 (Port 5)                               | 58              |

|              |        | 3.2.7 P60 to P67 (Port 6)                               | 58              |

|              |        |                                                         | 59              |

|              |        | 3.2.8 P70 to P72 (Port 7)                               | 59<br>59        |

|              |        | 3.2.10 P130 and P131 (Port 13)                          | 60              |

|              |        | 3.2.11 AVREF0                                           | 60              |

|              |        | 3.2.12 AVREF1                                           | 60              |

|              |        | 3.2.13 AVss                                             | 60              |

|              |        | 3.2.14 RESET                                            | 60              |

|              |        | 3.2.15 X1 and X2                                        |                 |

|              |        | 3.2.16 XT1 and XZ                                       | 60<br>60        |

|              |        |                                                         |                 |

|              |        | 3.2.17 VDD0, VDD1                                       | 60              |

|              |        | 3.2.18 Vsso, Vss1                                       | 61              |

|              |        | 3.2.19 Vpp (Flash memory version only)                  | 61              |

|              | 0.0    | 3.2.20 IC (Mask ROM version only)                       | 61<br><b>62</b> |

|              | ა.ა    | I/O CITCUITS AND DECOMMENDED COMMECTION OF UNIOSED PINS | 04              |

| CHAPT      | ER 4 P | IN FUNCTIONS (µPD780058Y SUBSERIES)              | 66         |

|------------|--------|--------------------------------------------------|------------|

| 4.1        | Pin Fu | unction List                                     | 66         |

| 4.2        | Descr  | iption of Pin Functions                          | 70         |

|            | 4.2.1  | P00 to P05, P07 (Port 0)                         | 70         |

|            | 4.2.2  | P10 to P17 (Port 1)                              | 71         |

|            | 4.2.3  | P20 to P27 (Port 2)                              | 71         |

|            | 4.2.4  | P30 to P37 (Port 3)                              | 72         |

|            | 4.2.5  | P40 to P47 (Port 4)                              | 73         |

|            | 4.2.6  | P50 to P57 (Port 5)                              | 73         |

|            | 4.2.7  | P60 to P67 (Port 6)                              | 73         |

|            | 4.2.8  | P70 to P72 (Port 7)                              | 74         |

|            | 4.2.9  | P120 to P127 (Port 12)                           | 74         |

| heet4U.com | 4.2.10 | ) P130 and P131 (Port 13)                        | 75         |

|            | 4.2.11 | 1 AVREF0                                         | 75         |

|            | 4.2.12 | 2 AVREF1                                         | 75         |

|            | 4.2.13 | 3 AVss                                           | 75         |

|            | 4.2.14 | 4 RESET                                          | 75         |

|            | 4.2.15 | 5 X1 and X2                                      | 75         |

|            | 4.2.16 | 3 XT1 and XT2                                    | 75         |

|            | 4.2.17 | 7 Vddo, Vdd1                                     | 75         |

|            | 4.2.18 | 3 Vsso, Vss1                                     | 76         |

|            | 4.2.19 | 9 VPP (Flash memory version only)                | 76         |

|            | 4.2.20 | O IC (Mask ROM version only)                     | 76         |

| 4.3        | I/O Ci | rcuits and Recommended Connection of Unused Pins | 77         |

| OLLADZ     |        | DIL ABOUTESTURE                                  | 0.4        |

|            |        | PU ARCHITECTURE                                  | 81         |

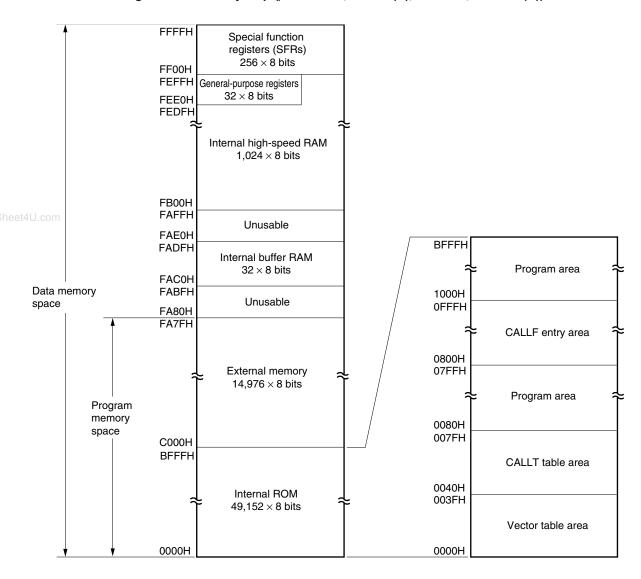

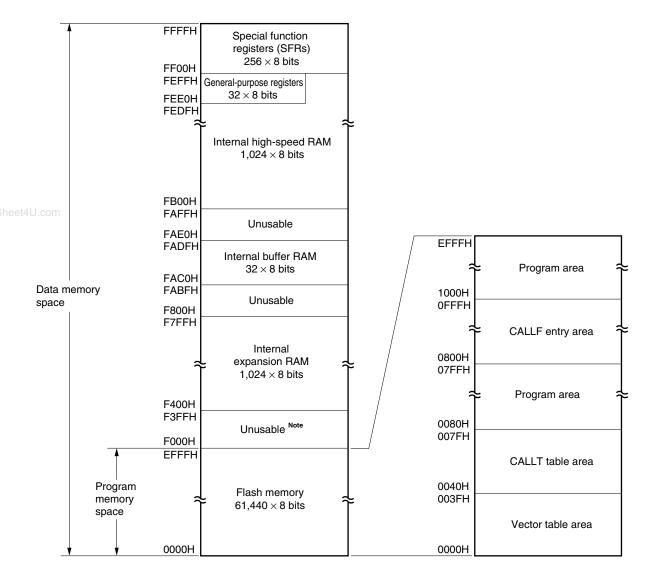

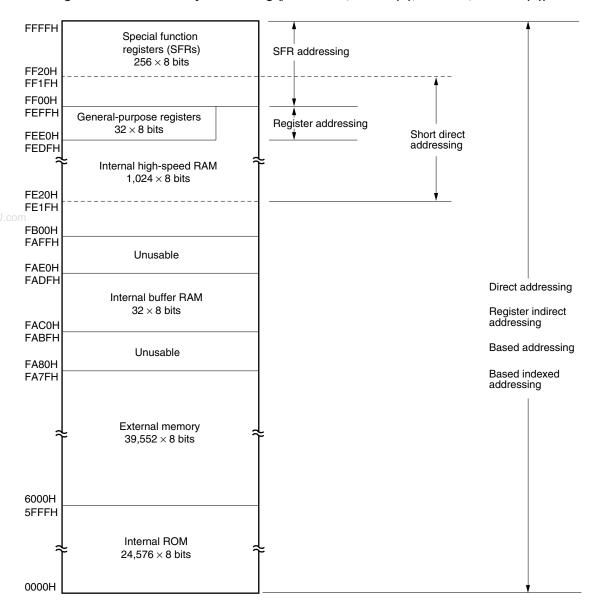

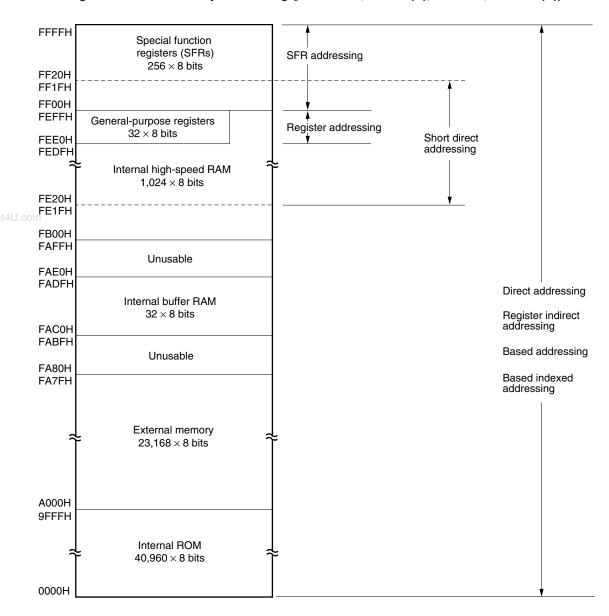

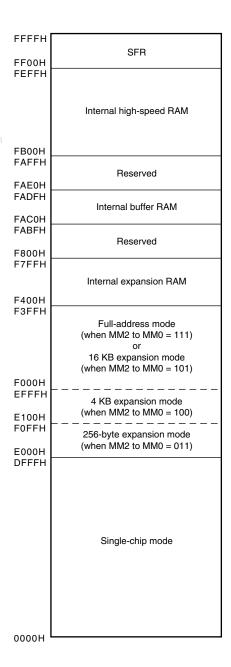

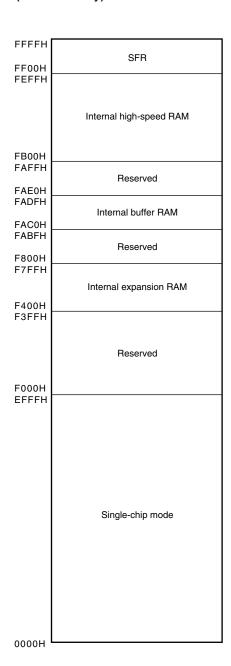

| 5.1        |        | ry Spaces                                        | 81         |

|            |        | Internal program memory space                    | 87         |

|            |        | Internal data memory space                       | 89         |

|            |        | Special Function Register (SFR) area             | 89         |

|            |        | External memory space                            | 89         |

| F (        |        | Data memory addressing                           | 89         |

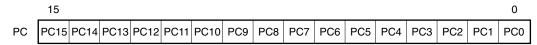

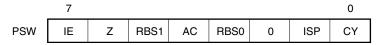

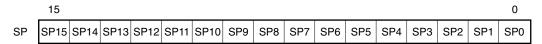

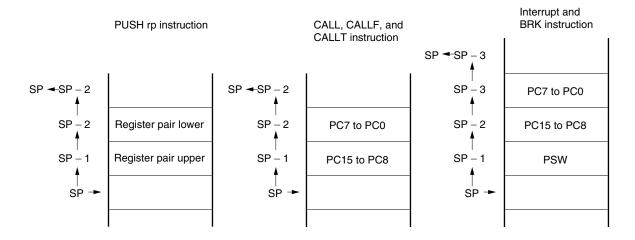

| 5.4        |        | ssor Registers                                   | 96         |

|            |        | Control registers                                | 96         |

|            |        | General registers                                | 99         |

| F (        |        | Special-Function Registers (SFRs)                | 100        |

| 5.3        |        | ction Address Addressing                         | 104        |

|            |        | Relative addressing                              | 104        |

|            |        | Immediate addressing                             | 105        |

|            |        | Table indirect addressing                        | 106        |

| <b>5</b> / |        | Register addressing                              | 107        |

| 5.4        | •      | •                                                | 108        |

|            |        | Implied addressing                               | 108        |

|            |        | Register addressing                              | 109        |

|            |        | Direct addressing                                | 110        |

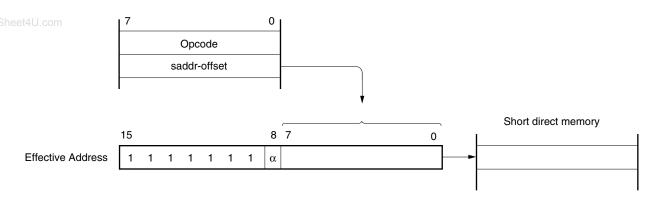

|            |        | Short direct addressing                          | 111        |

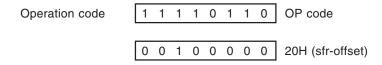

|            |        | Special-Function Register (SFR) addressing       | 113        |

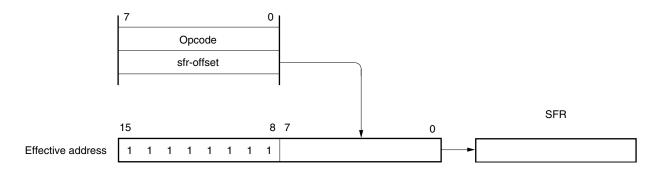

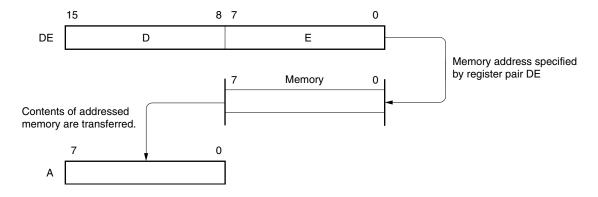

|            |        | Register indirect addressing  Based addressing   | 114<br>115 |

|            | :14/   | DOSEU OUUESSIUU                                  | 110        |

|        | 5.4.8 Based indexed addressing                                        | 116 |

|--------|-----------------------------------------------------------------------|-----|

|        | 5.4.9 Stack addressing                                                | 116 |

|        |                                                                       |     |

|        | ER 6 PORT FUNCTIONS                                                   |     |

|        | Port Functions                                                        |     |

| 6.2    | Port Configuration                                                    |     |

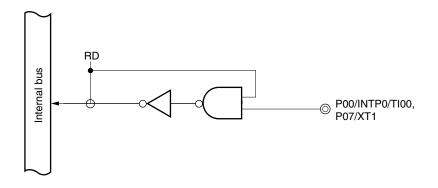

|        | 6.2.1 Port 0                                                          |     |

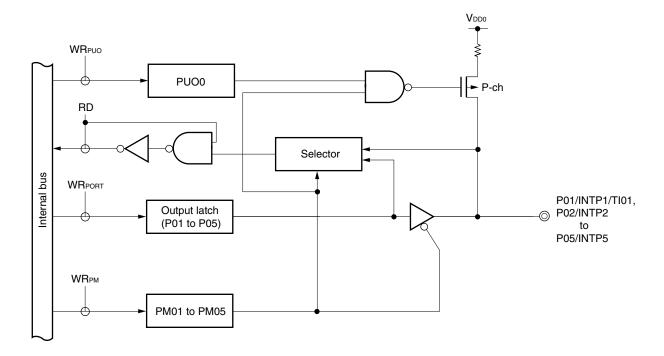

|        | 6.2.2 Port 1                                                          |     |

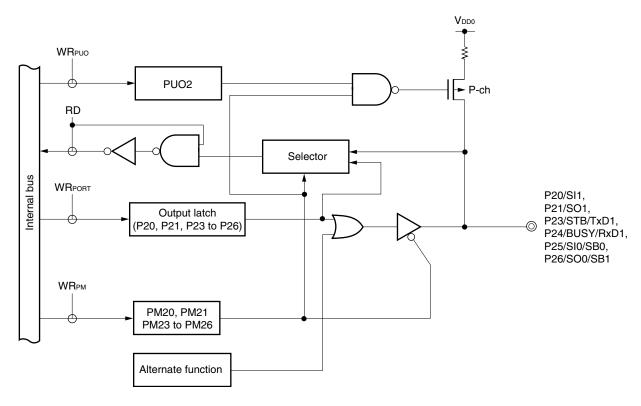

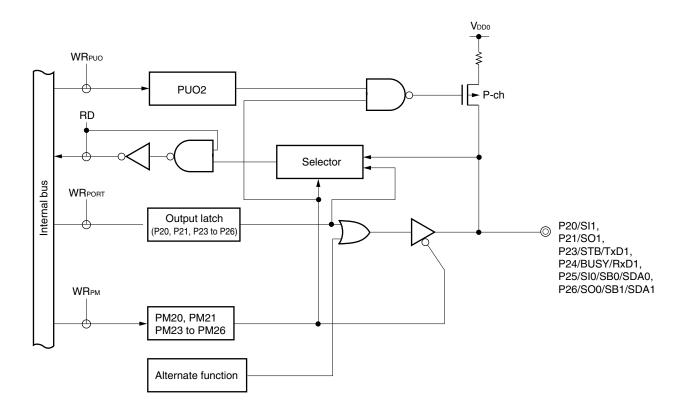

|        | 6.2.3 Port 2 (μPD780058 Subseries)                                    |     |

|        | 6.2.4 Port 2 (μPD780058Y Subseries)                                   |     |

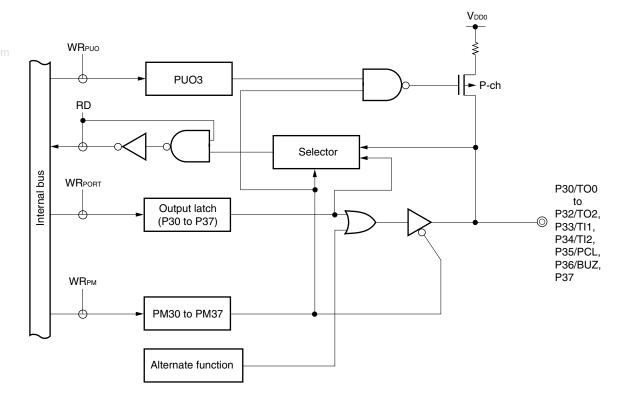

|        | 6.2.5 Port 3                                                          |     |

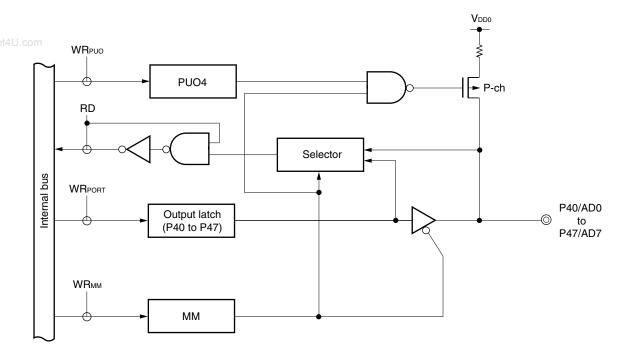

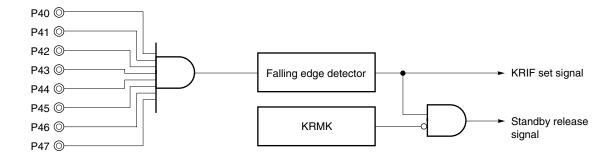

|        | 6.2.6 Port 4                                                          |     |

|        | 6.2.7 Port 5                                                          | _   |

|        | 6.2.8 Port 6                                                          |     |

|        | 6.2.9 Port 7                                                          |     |

|        | 6.2.10 Port 12                                                        |     |

| 6.2    | 6.2.11 Port 13                                                        |     |

|        | Port Constitute                                                       |     |

| 0.4    | Port Operations                                                       |     |

|        | 6.4.2 Reading from I/O port                                           |     |

|        | 6.4.3 Operations on I/O port                                          |     |

| 6.5    | Selection of Mask Option                                              |     |

| 0.5    | delection of mask option                                              |     |

| CHAPTI | ER 7 CLOCK GENERATOR                                                  | 146 |

| 7.1    | Clock Generator Functions                                             | 146 |

| 7.2    | Clock Generator Configuration                                         | 146 |

| 7.3    | Clock Generator Control Registers                                     | 148 |

| 7.4    | System Clock Oscillator                                               | 152 |

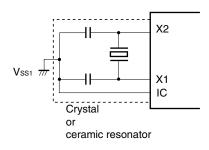

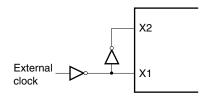

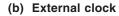

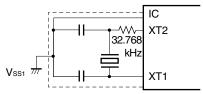

|        | 7.4.1 Main system clock oscillator                                    | 152 |

|        | 7.4.2 Subsystem clock oscillator                                      | 153 |

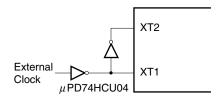

|        | 7.4.3 Example of resonator with bad connection                        | 154 |

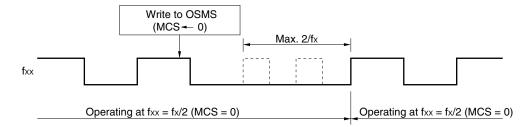

|        | 7.4.4 Divider                                                         | 155 |

|        | 7.4.5 When not using subsystem clock                                  | 155 |

| 7.5    | Clock Generator Operations                                            | 156 |

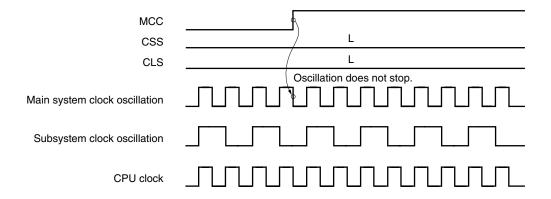

|        | 7.5.1 Main system clock operations                                    | 157 |

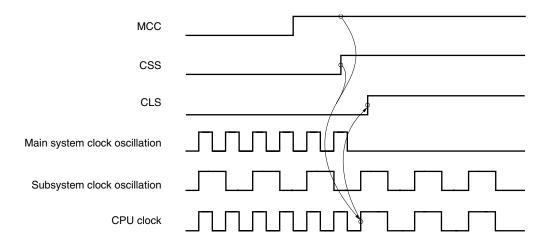

|        | 7.5.2 Subsystem clock operations                                      |     |

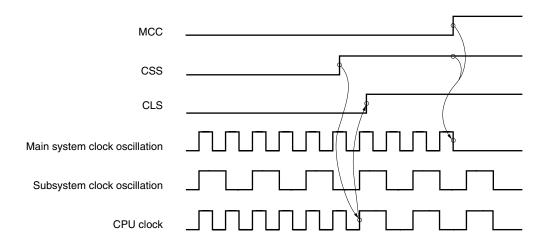

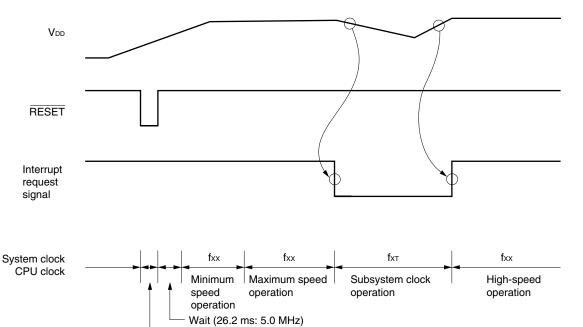

| 7.6    | Changing System Clock and CPU Clock Settings                          |     |

|        | 7.6.1 Time required for switchover between system clock and CPU clock |     |

|        | 7.6.2 System clock and CPU clock switching procedure                  | 161 |

| СНАВТ  | ER 8 16-BIT TIMER/EVENT COUNTER                                       | 162 |

|        | 16-Bit Timer/Event Counter Functions                                  |     |

|        | 16-Bit Timer/Event Counter Configuration                              |     |

|        | 16-Bit Timer/Event Counter Control Registers                          |     |

|        | 16-Bit Timer/Event Counter Operations                                 |     |

| 0.4    | 8.4.1 Interval timer operations                                       |     |

|        | 8.4.2 PWM output operations                                           |     |

|        | 8.4.3 PPG output operations                                           |     |

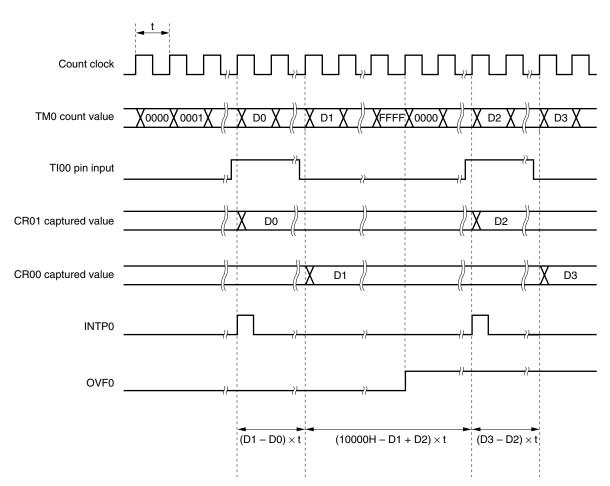

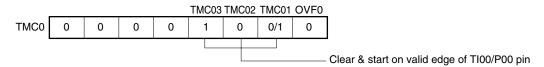

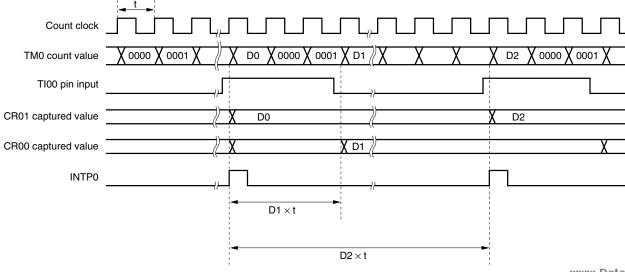

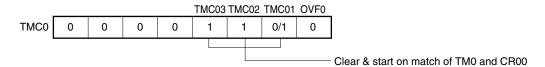

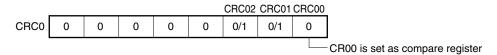

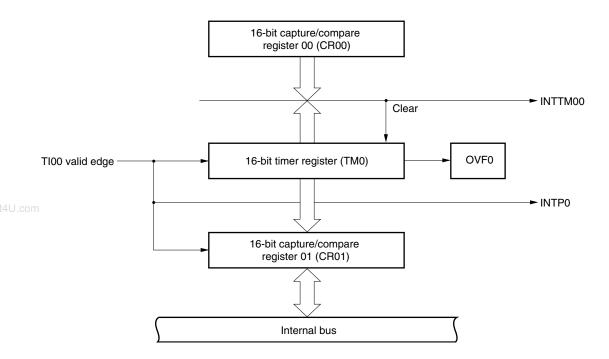

|        | 8 4 4 Pulse width measurement operations                              | 186 |

|             | 8.4.5 External event counter operation           | 193 |

|-------------|--------------------------------------------------|-----|

|             | 8.4.6 Square-wave output operation               | 195 |

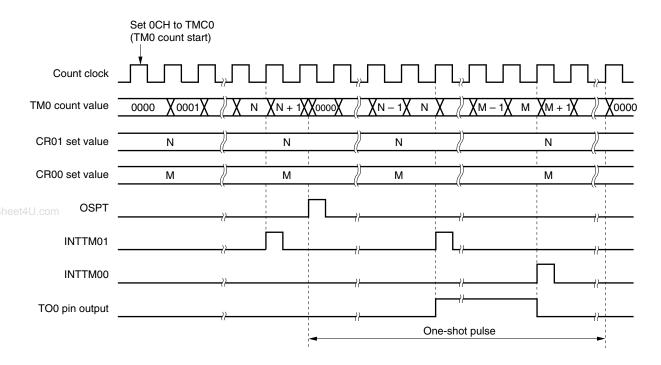

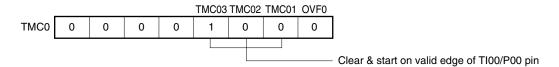

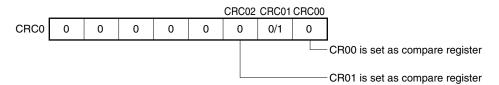

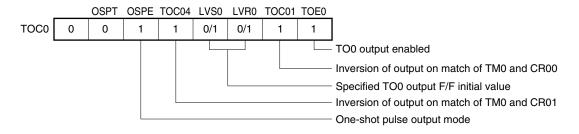

|             | 8.4.7 One-shot pulse output operation            | 197 |

| 8.5         | 16-Bit Timer/Event Counter Operating Cautions    | 201 |

| CHAPTE      | R 9 8-BIT TIMER/EVENT COUNTER                    | 205 |

| 9.1         | 8-Bit Timer/Event Counter Functions              | 205 |

|             | 9.1.1 8-bit timer/event counter mode             | 205 |

|             | 9.1.2 16-bit timer/event counter mode            | 208 |

| 9.2         | 8-Bit Timer/Event Counter Configuration          | 210 |

| 9.3         | 8-Bit Timer/Event Counter Control Registers      | 214 |

| 9.4         | Operations of 8-Bit Timer/Event Counters 1 and 2 | 219 |

| Sheet4U.com | 9.4.1 8-bit timer/event counter mode             | 219 |

|             | 9.4.2 16-bit timer/event counter mode            | 225 |

| 9.5         | Cautions on 8-Bit Timer/Event Counters 1 and 2   | 230 |

| CHAPTE      | R 10 WATCH TIMER                                 | 232 |

| 10.1        | Watch Timer Functions                            | 232 |

| 10.2        | Watch Timer Configuration                        | 233 |

| 10.3        | Watch Timer Control Registers                    | 233 |

| 10.4        | Watch Timer Operations                           | 237 |

|             | 10.4.1 Watch timer operation                     | 237 |

|             | 10.4.2 Interval timer operation                  | 237 |

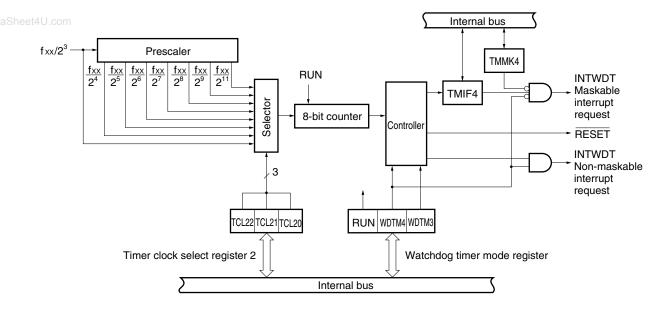

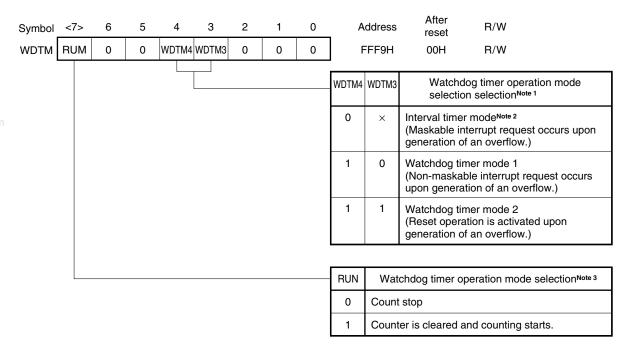

| CHAPTE      | R 11 WATCHDOG TIMER                              | 238 |

| 11.1        | Watchdog Timer Functions                         | 238 |

| 11.2        | Watchdog Timer Configuration                     | 240 |

| 11.3        | Watchdog Timer Control Registers                 | 241 |

| 11.4        | Watchdog Timer Operations                        | 244 |

|             | 11.4.1 Watchdog timer operation                  | 244 |

|             | 11.4.2 Interval timer operation                  | 245 |

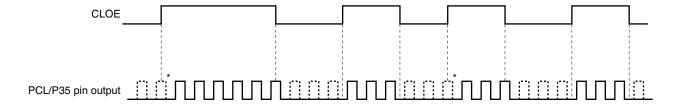

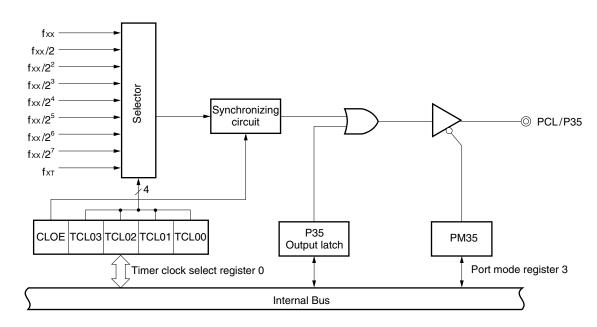

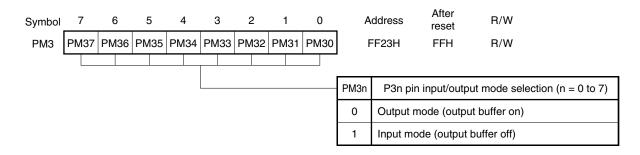

| CHAPTE      | R 12 CLOCK OUTPUT CONTROLLER                     | 246 |

| 12.1        | Clock Output Controller Functions                | 246 |

|             | Clock Output Controller Configuration            |     |

| 12.3        | Clock Output Function Control Registers          | 247 |

| CHAPTE      | R 13 BUZZER OUTPUT CONTROLLER                    | 250 |

| 13.1        | Buzzer Output Controller Functions               | 250 |

| 13.2        | Buzzer Output Controller Configuration           | 250 |

| 13.3        | Buzzer Output Function Control Registers         | 251 |

|             | R 14 A/D CONVERTER                               | 254 |

| 14.1        | A/D Converter Functions                          | 254 |

| 14.2        | A/D Converter Configuration                      | 254 |

| 14.3        | A/D Converter Control Registers                  | 258 |

| 14.4        | A/D Converter Operations                         | 262 |

|             | 14.4.1 Basic operations of A/D converter         | 262 |

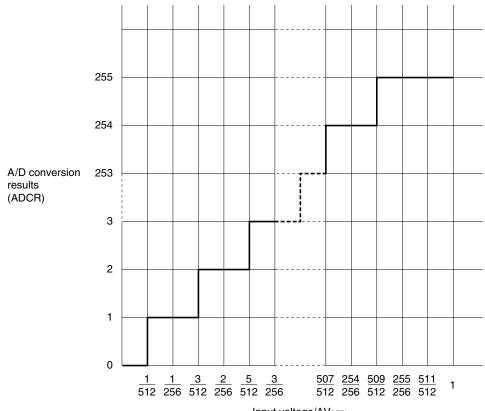

|             | 14.4.2 Input voltage and conversion results      | 264 |

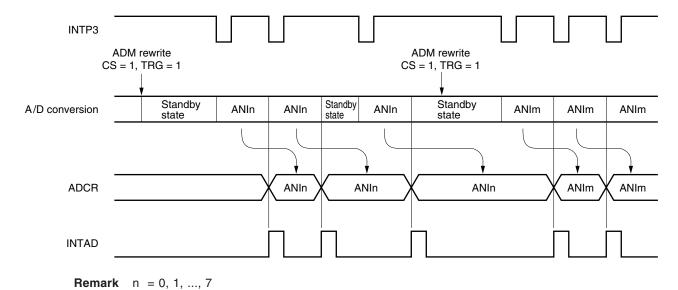

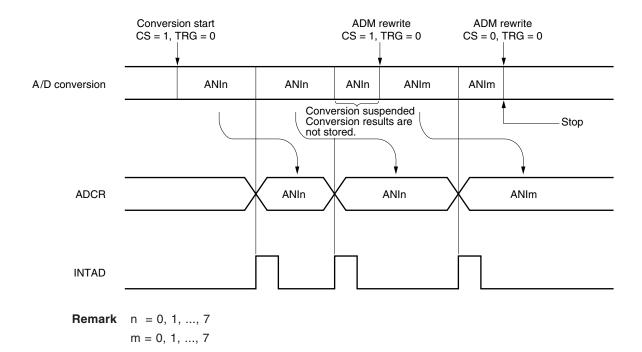

|             | 14.4.3 A/D converter operating mode              | 265 |

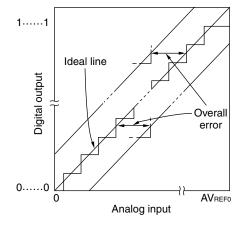

| *               | 14.5   | How to Read the A/D Converter Characteristics Table                              | 267 |

|-----------------|--------|----------------------------------------------------------------------------------|-----|

|                 | 14.6   | A/D Converter Cautions                                                           | 269 |

|                 | CHAPTE | R 15 D/A CONVERTER                                                               | 275 |

|                 |        | D/A Converter Functions                                                          |     |

|                 | 15.2   | D/A Converter Configuration                                                      | 276 |

|                 |        | D/A Converter Control Registers                                                  |     |

|                 |        | D/A Converter Operations                                                         |     |

|                 |        | D/A Converter Cautions                                                           |     |

|                 | CHARTE | R 16 SERIAL INTERFACE CHANNEL 0 (µPD780058 SUBSERIES)                            | 201 |

|                 |        | Functions of Serial Interface Channel 0                                          |     |

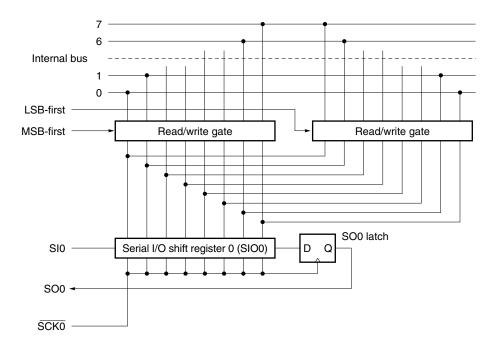

|                 |        | Configuration of Serial Interface Channel 0                                      |     |

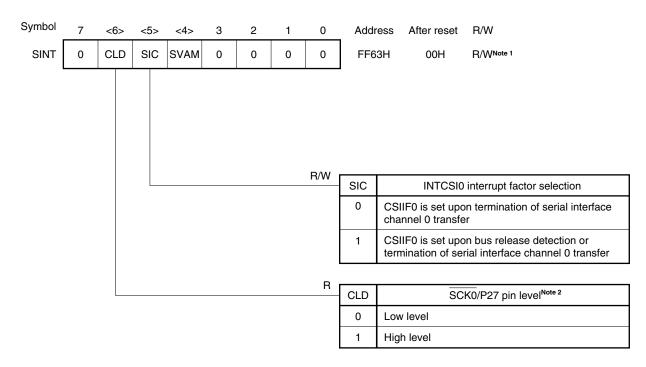

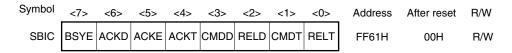

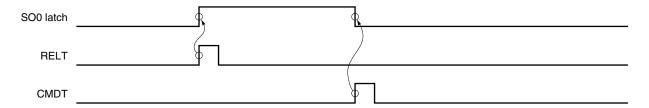

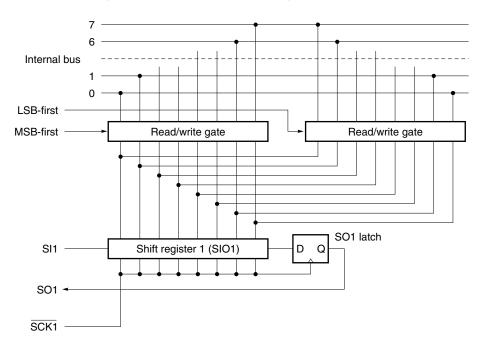

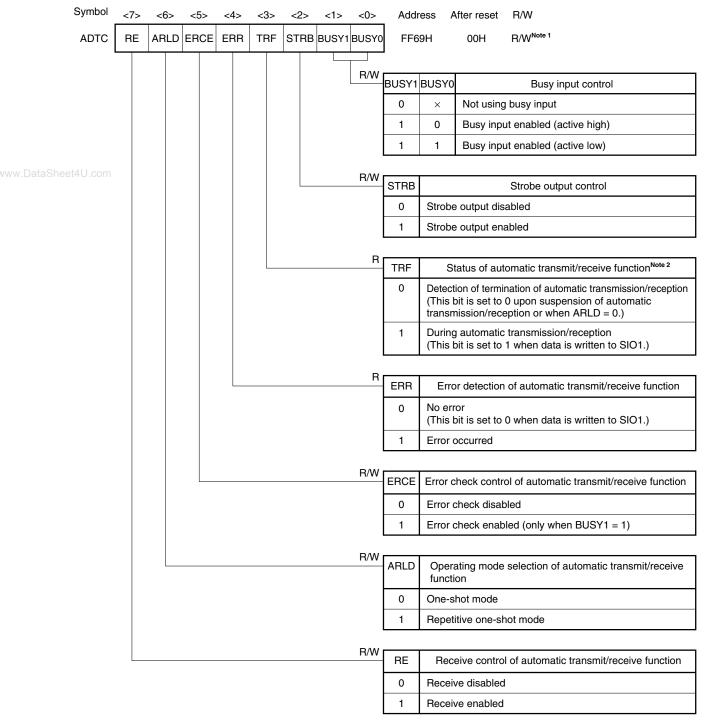

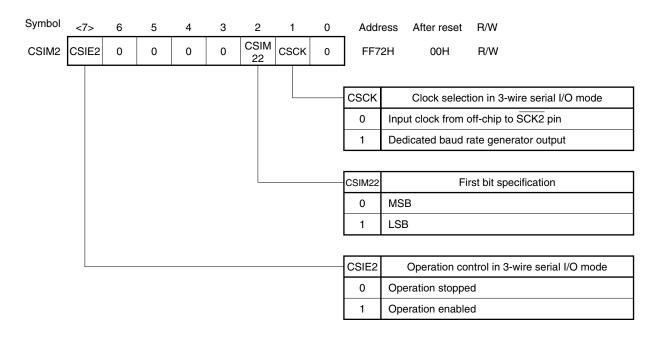

| DataSheet4U.con |        | Control Registers of Serial Interface Channel 0                                  |     |

|                 |        | Operations of Serial Interface Channel 0                                         |     |

|                 | 10.4   | 16.4.1 Operation stop mode                                                       |     |

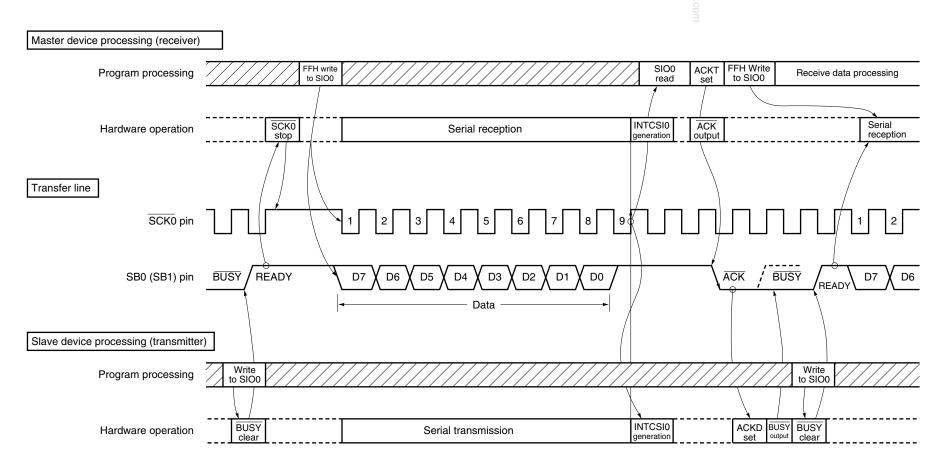

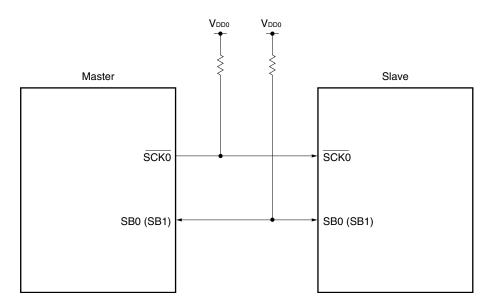

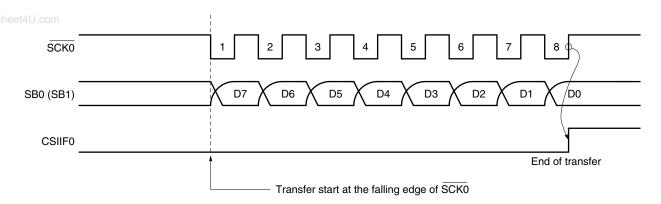

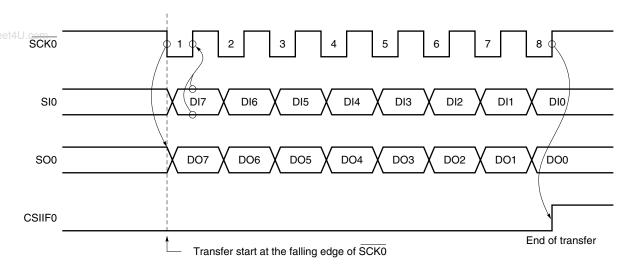

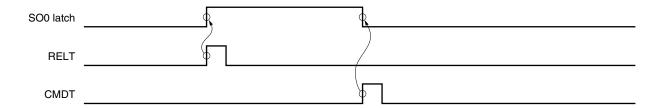

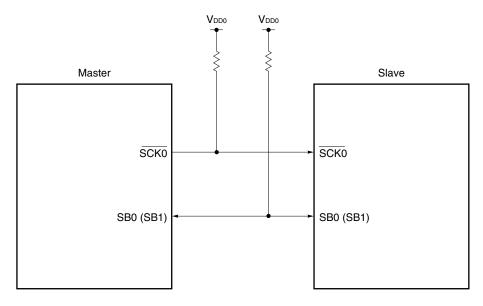

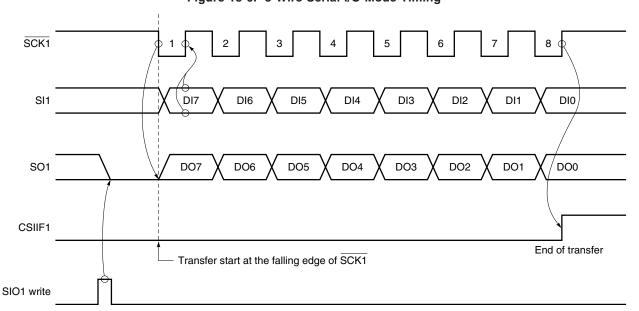

|                 |        | 16.4.2 3-wire serial I/O mode operation                                          |     |

|                 |        | 16.4.3 SBI mode operation                                                        |     |

|                 |        | 16.4.4 2-wire serial I/O mode operation                                          |     |

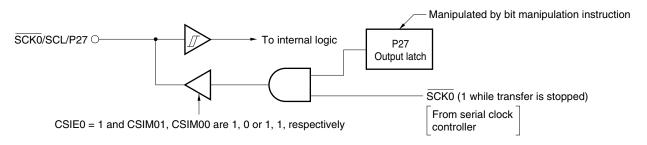

|                 |        | 16.4.5 SCK0/P27 pin output manipulation                                          |     |

|                 |        | 10.4.0 GONO/1 27 pin output manipulation                                         | 002 |

|                 | CHAPTE | R 17 SERIAL INTERFACE CHANNEL 0 (µPD780058Y SUBSERIES)                           | 333 |

|                 | 17.1   | Functions of Serial Interface Channel 0                                          | 334 |

|                 | 17.2   | Configuration of Serial Interface Channel 0                                      | 336 |

|                 |        | Control Registers of Serial Interface Channel 0                                  |     |

|                 | 17.4   | Operations of Serial Interface Channel 0                                         |     |

|                 |        | 17.4.1 Operation stop mode                                                       |     |

|                 |        | 17.4.2 3-wire serial I/O mode operation                                          |     |

|                 |        | 17.4.3 2-wire serial I/O mode operation                                          |     |

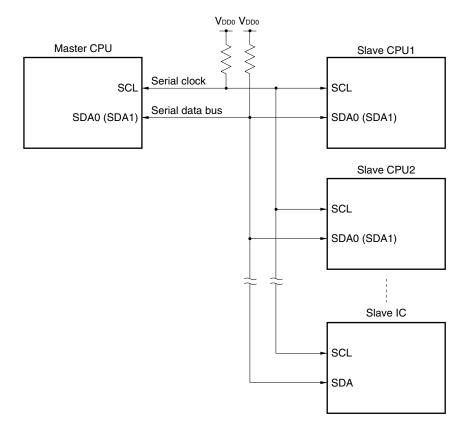

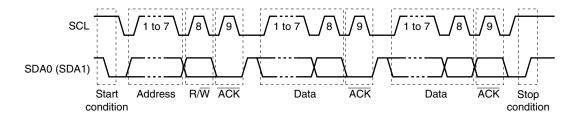

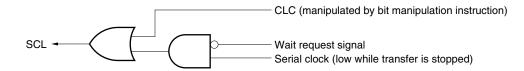

|                 |        | 17.4.4 I <sup>2</sup> C bus mode operation                                       |     |

|                 |        | 17.4.5 Cautions on use of I <sup>2</sup> C bus mode                              |     |

|                 |        | 17.4.6 Restrictions in I <sup>2</sup> C bus mode 1                               |     |

|                 |        | 17.4.7 Restrictions in I <sup>2</sup> C bus mode 2                               |     |

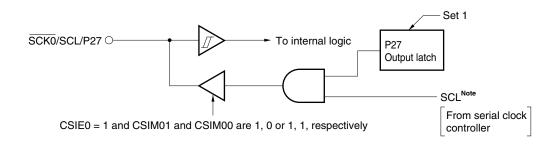

|                 |        | 17.4.8 SCK0/SCL/P27 pin output manipulation                                      | 380 |

|                 | CHAPTE | R 18 SERIAL INTERFACE CHANNEL 1                                                  | 382 |

|                 | 18.1   | Functions of Serial Interface Channel 1                                          | 382 |

|                 |        | Configuration of Serial Interface Channel 1                                      |     |

|                 |        | Control Registers of Serial Interface Channel 1                                  |     |

|                 | 18.4   | Operations of Serial Interface Channel 1                                         |     |

|                 |        | 18.4.1 Operation stop mode                                                       |     |

|                 |        | 18.4.2 3-wire serial I/O mode operation                                          |     |

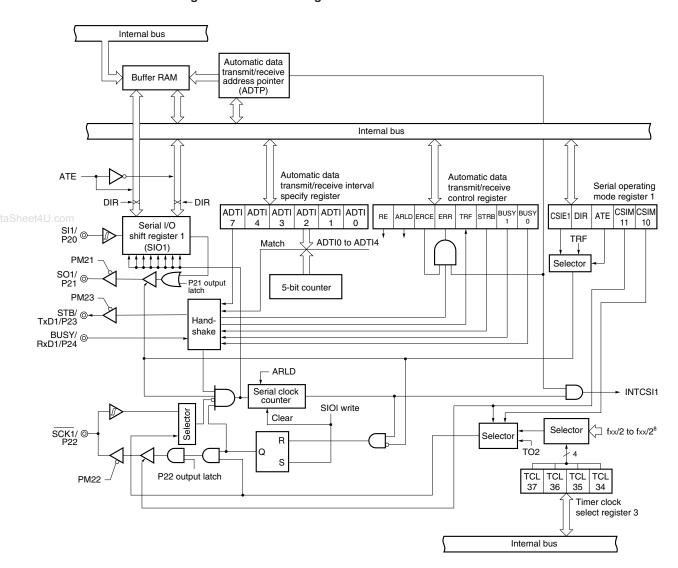

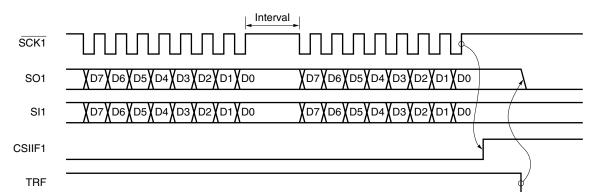

|                 |        | 18.4.3 3-wire serial I/O mode operation with automatic transmit/receive function | 398 |

|                 | CHAPTE | R 19 SERIAL INTERFACE CHANNEL 2                                                  | 427 |

|                 | 19.1   | Functions of Serial Interface Channel 2                                          | 427 |

|                 |        | Configuration of Serial Interface Channel 2                                      |     |

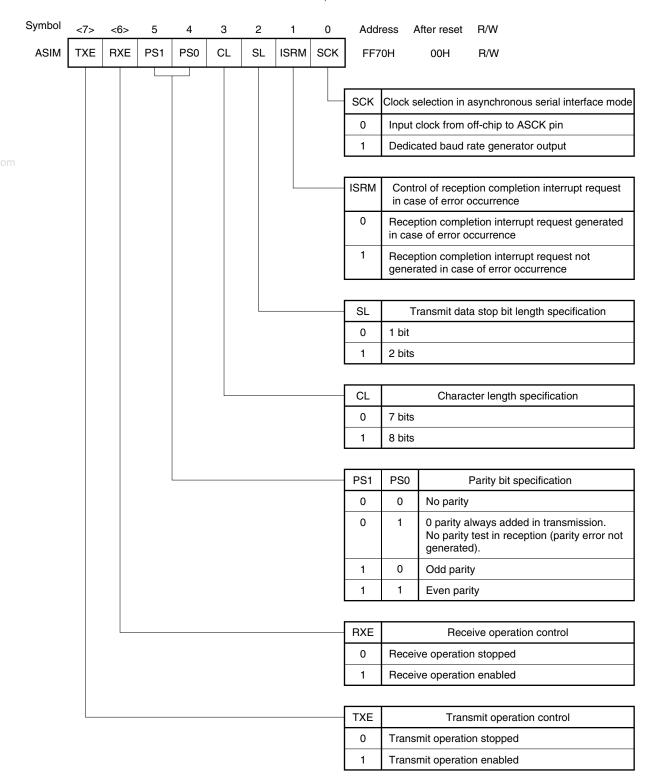

|                 | 19.3   | Control Registers of Serial Interface Channel 2                                  | 432 |

|                 | 19.4   | Operation of Serial Interface Channel 2                                          | 442 |

19.4.1 Operation stop mode.....

|                | 19.4.2 Asynchronous serial interface (UAH1) mode (with time-division transfer function) | 444 |

|----------------|-----------------------------------------------------------------------------------------|-----|

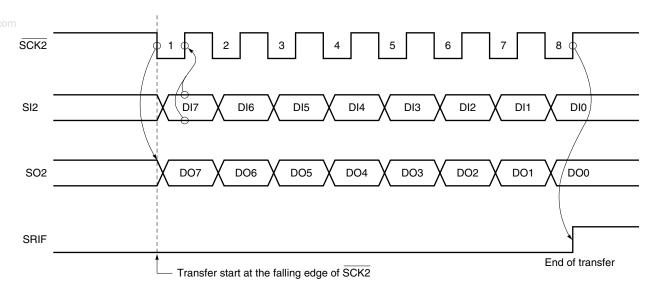

|                | 19.4.3 3-wire serial I/O mode                                                           | 458 |

|                | 19.4.4 Restrictions in UART mode 1                                                      | 465 |

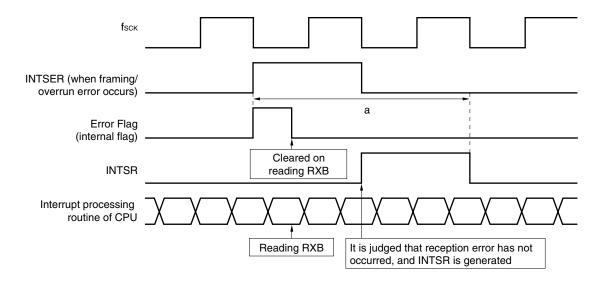

| *              | 19.4.5 Restrictions in UART mode 2                                                      | 468 |

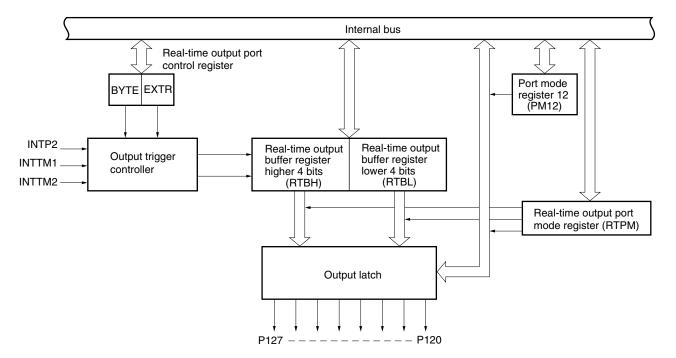

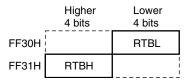

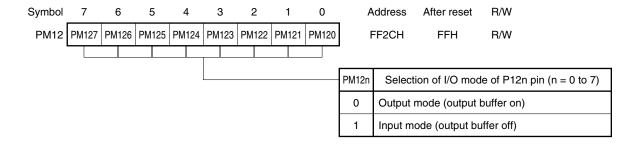

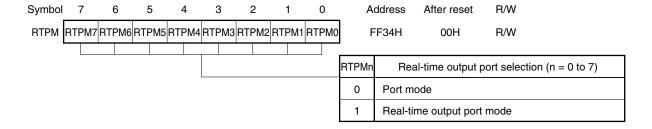

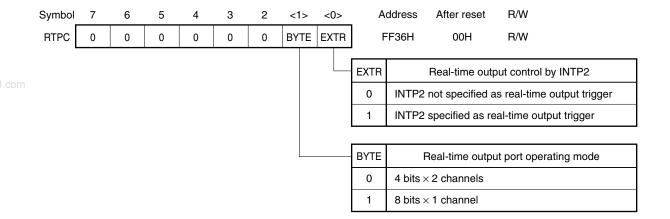

| CHAPTE         | R 20 REAL-TIME OUTPUT PORT                                                              | 469 |

|                | Real-Time Output Port Functions                                                         | 469 |

|                | Real-Time Output Port Configuration                                                     |     |

|                | Real-Time Output Port Control Registers                                                 | 472 |

| 20.0           | Tiour Time Output Fort Control Hegisters                                                | 772 |

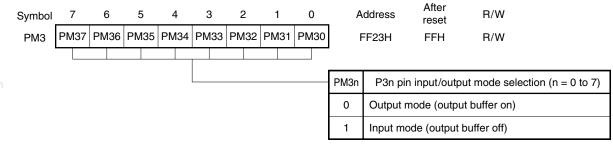

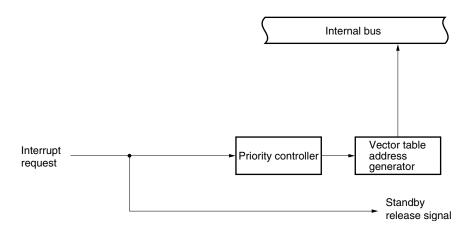

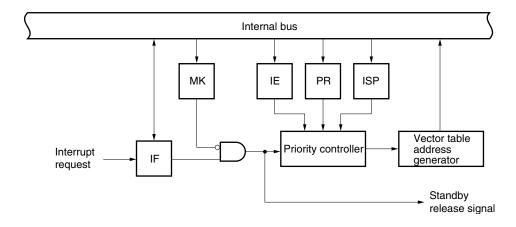

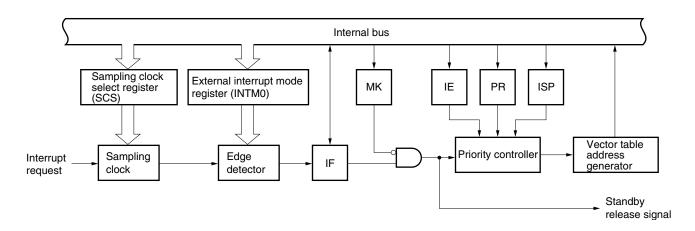

| CHAPTE         | R 21 INTERRUPT AND TEST FUNCTIONS                                                       | 474 |

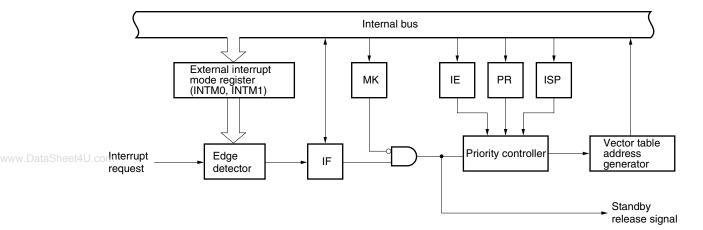

| 21.1           | Interrupt Function Types                                                                | 474 |

| 21.2           | Interrupt Sources and Configuration                                                     | 475 |

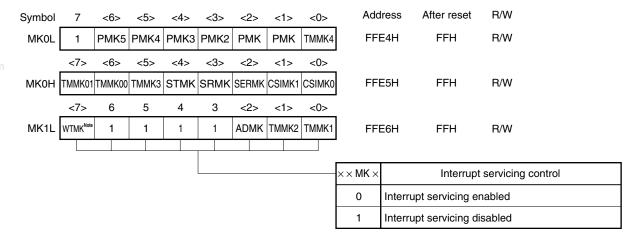

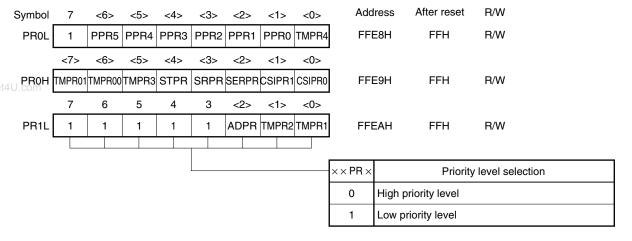

| ataSheet4U.com | Interrupt Function Control Registers                                                    | 479 |

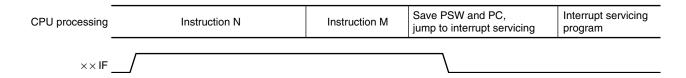

|                | Interrupt Servicing Operations                                                          | 488 |

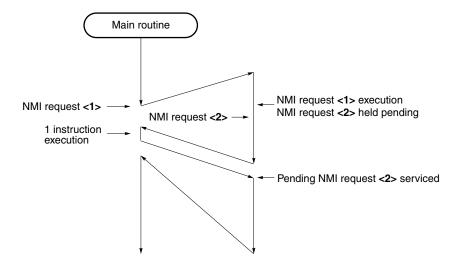

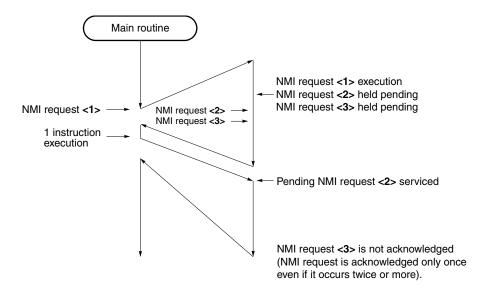

|                | 21.4.1 Non-maskable interrupt request acknowledgment operation                          | 488 |

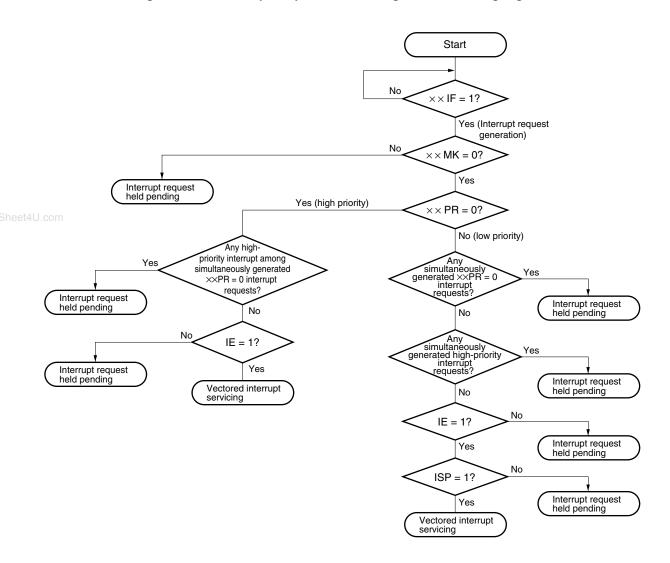

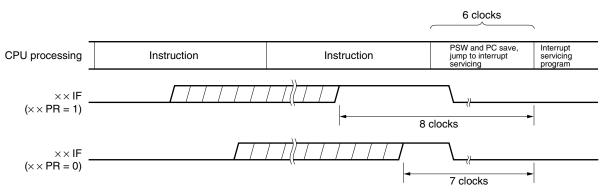

|                | 21.4.2 Maskable interrupt request acknowledgment operation                              | 491 |

|                | 21.4.3 Software interrupt request acknowledgment operation                              | 494 |

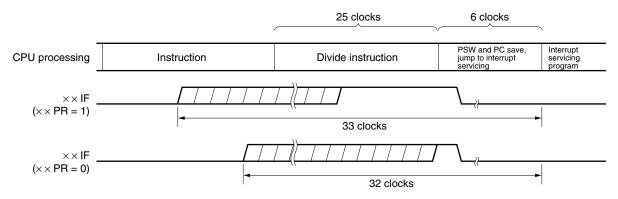

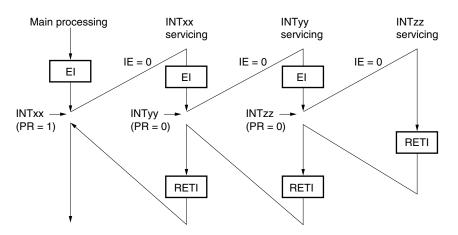

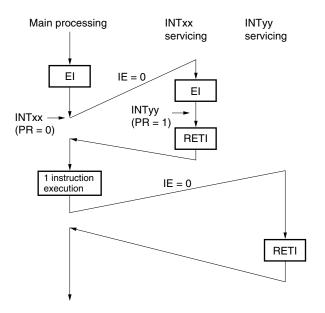

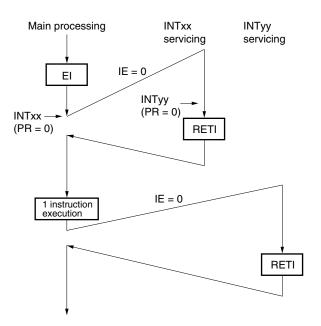

|                | 21.4.4 Multiple interrupt servicing                                                     | 494 |

|                | 21.4.5 Interrupt request pending                                                        | 497 |

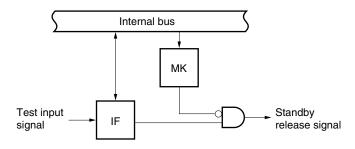

| 21.5           | Test Function                                                                           | 498 |

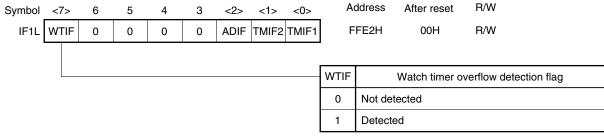

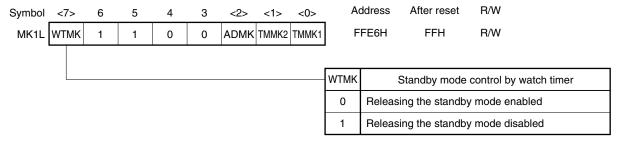

|                | 21.5.1 Registers controlling test function                                              | 498 |

|                | 21.5.2 Test input signal acknowledgment operation                                       | 500 |

| CHARTE         | R 22 EXTERNAL DEVICE EXPANSION FUNCTION                                                 | 501 |

|                | External Device Expansion Function                                                      |     |

|                | External Device Expansion Function Control Register                                     |     |

|                | External Device Expansion Function Control Register                                     |     |

|                | Example of Connection with Memory                                                       |     |

| 22.7           | Example of Confidence with Memory                                                       | 312 |

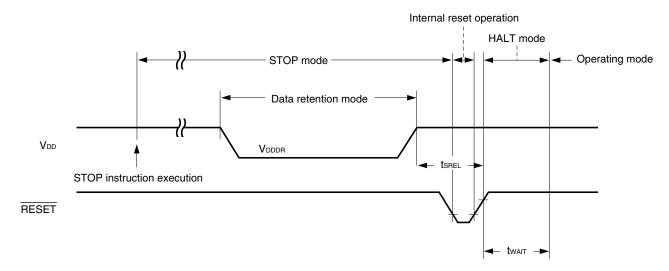

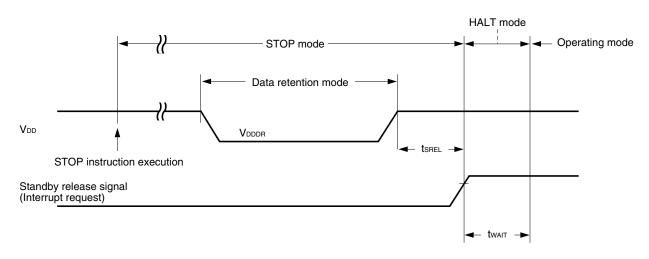

|                | R 23 STANDBY FUNCTION                                                                   |     |

| 23.1           | Standby Function and Configuration                                                      | 513 |

|                | 23.1.1 Standby function                                                                 | 513 |

|                | 23.1.2 Standby function control register                                                | 514 |

| 23.2           | Standby Function Operations                                                             | 515 |

|                | 23.2.1 HALT mode                                                                        | 515 |

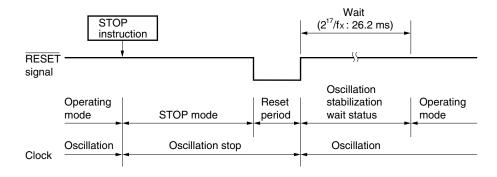

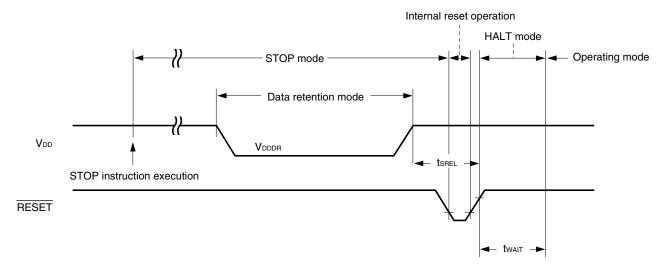

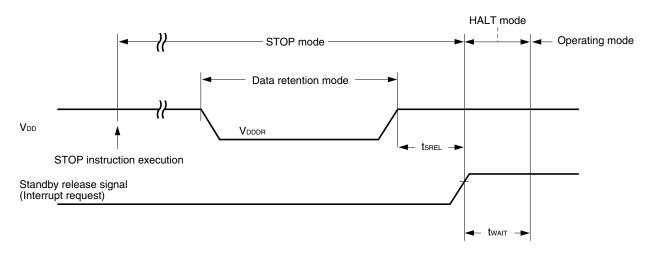

|                | 23.2.2 STOP mode                                                                        | 518 |

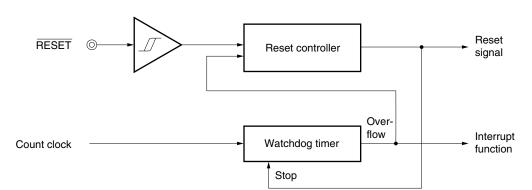

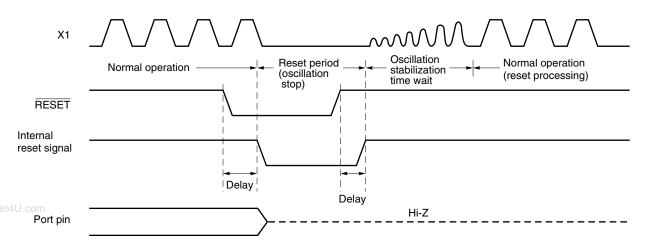

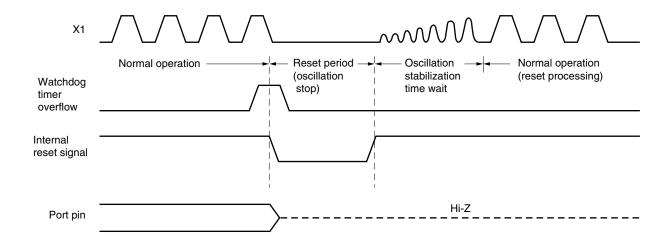

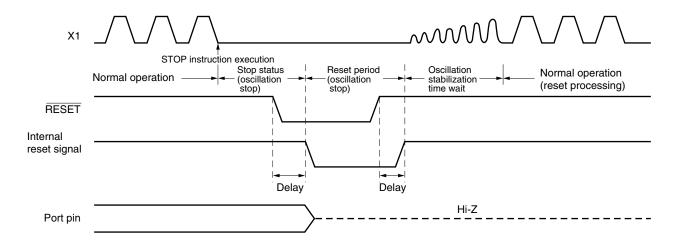

| CHAPTE         | R 24 RESET FUNCTION                                                                     | 521 |

|                | Reset Function                                                                          | 521 |

|                |                                                                                         |     |

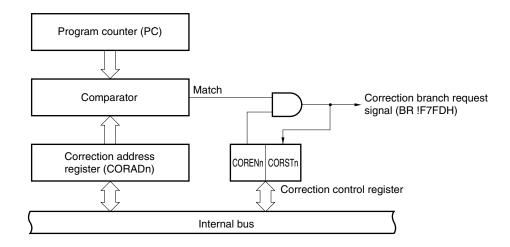

|                | R 25 ROM CORRECTION                                                                     | 525 |

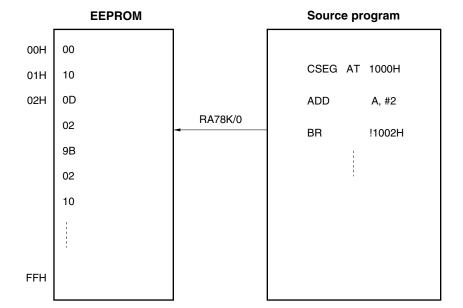

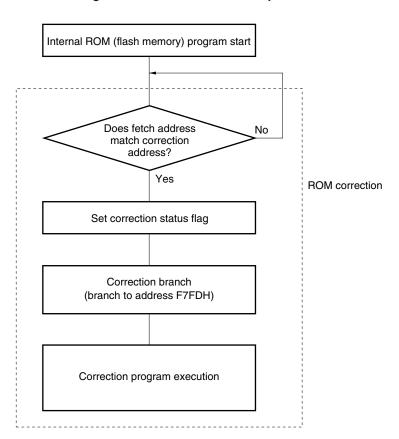

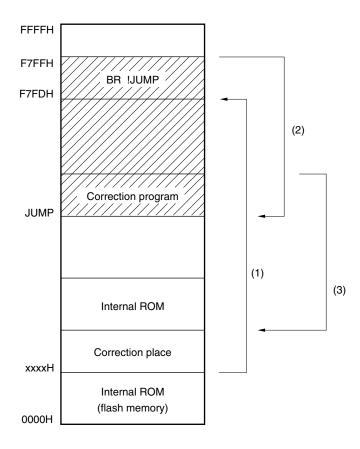

|                | ROM Correction Function                                                                 | 525 |

|                | ROM Correction Configuration                                                            | 525 |

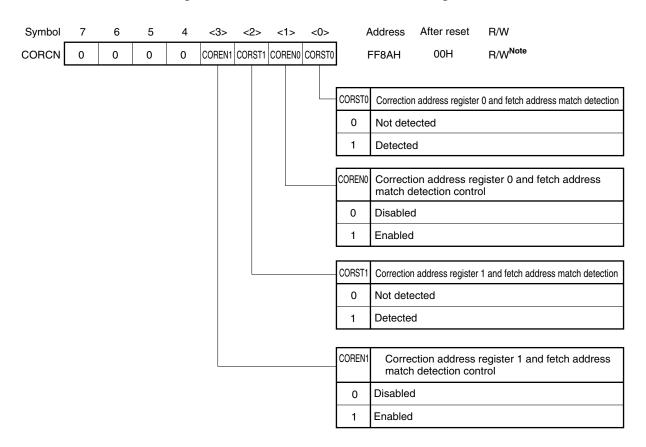

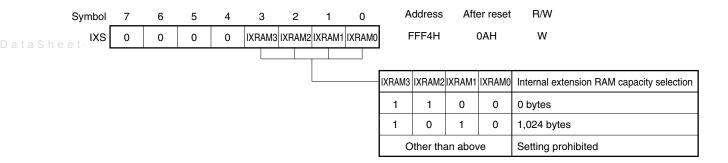

|                | ROM Correction Control Registers                                                        | 527 |

|                | ROM Correction Application                                                              | 528 |

|                | ROM Correction Usage Example                                                            | 531 |

|                | Program Execution Flow                                                                  | 532 |

| 25.7           | POM Correction Courtiens                                                                | E2/ |

|            | CHAPTER 26 $\mu$ PD78F0058, 78F0058Y                                                                          | 535 |

|------------|---------------------------------------------------------------------------------------------------------------|-----|

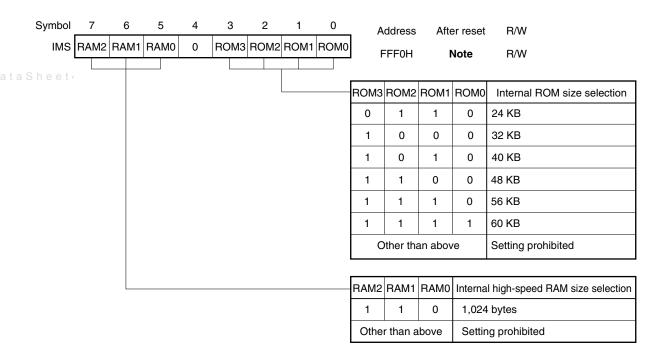

|            | 26.1 Internal memory Size Switching Register                                                                  | 536 |

|            | 26.2 Internal Expansion RAM Size Switching Register                                                           | 537 |

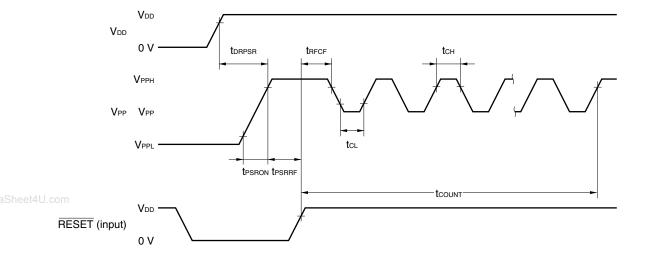

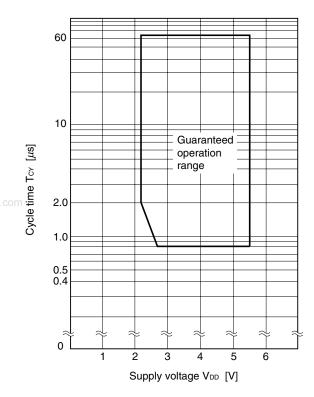

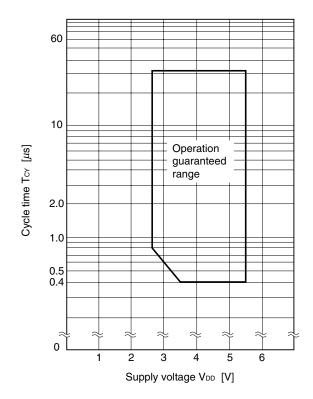

|            | 26.3 Flash Memory Characteristics                                                                             | 538 |

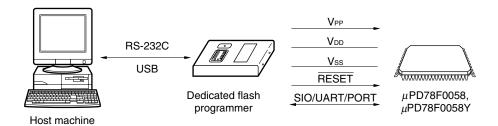

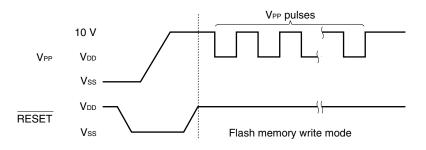

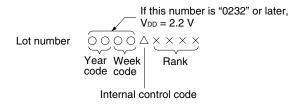

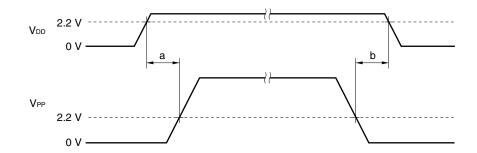

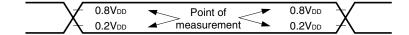

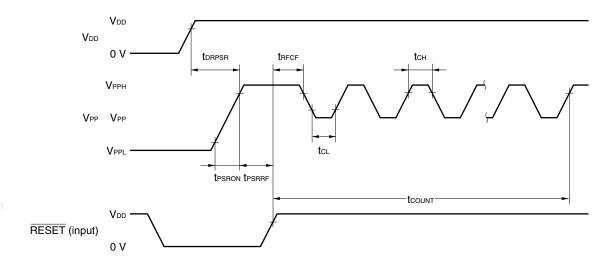

|            | 26.3.1 Programming environment                                                                                | 538 |

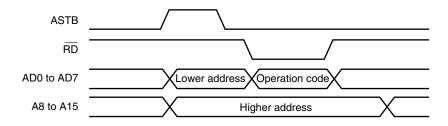

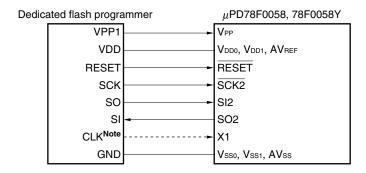

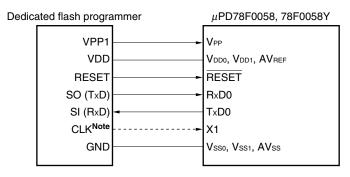

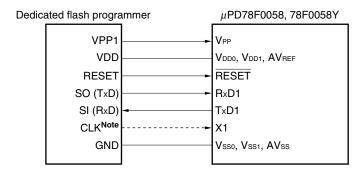

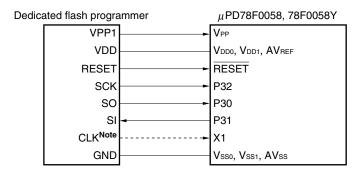

|            | 26.3.2 Communication mode                                                                                     | 539 |

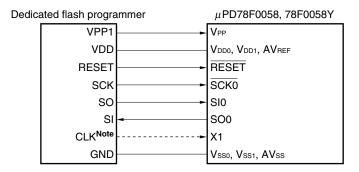

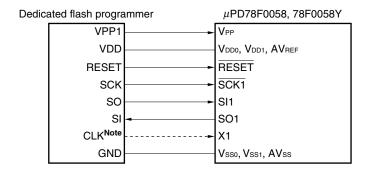

|            | 26.3.3 On-board pin processing                                                                                | 543 |

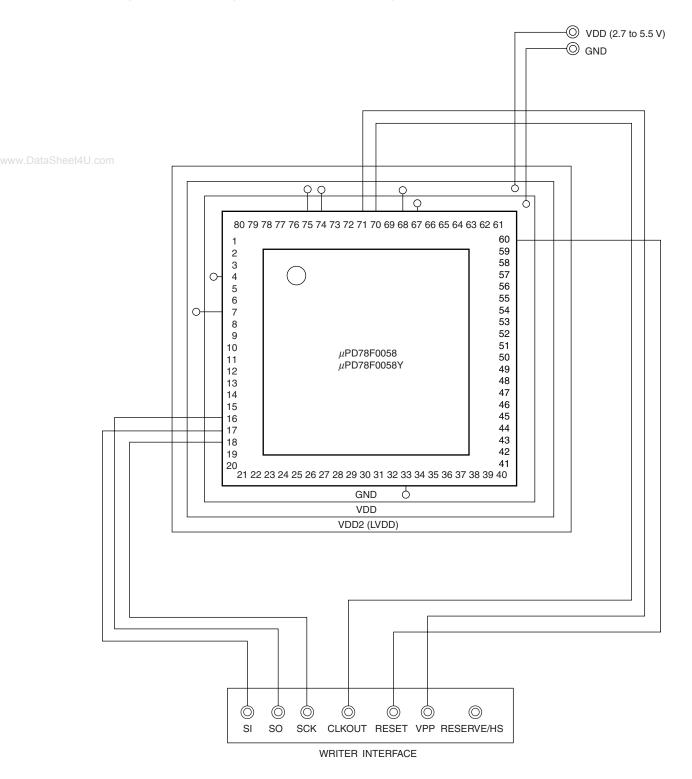

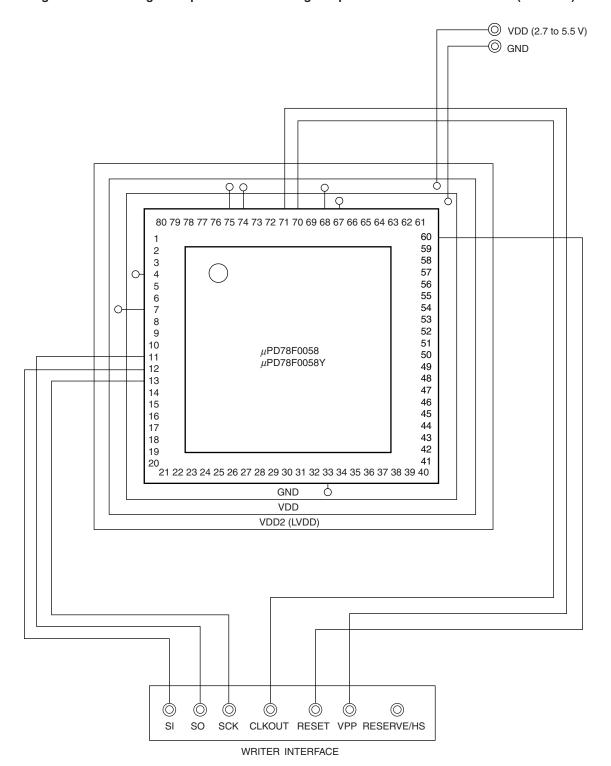

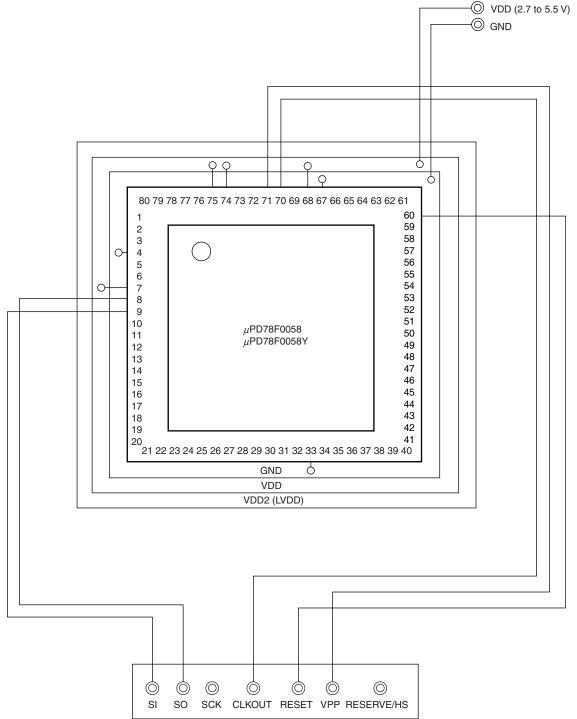

|            | 26.3.4 Connection of adapter for flash writing                                                                | 546 |

|            | CHAPTER 27 INSTRUCTION SET OVERVIEW                                                                           | 552 |

|            | 27.1 Conventions Used in Operation List                                                                       | 553 |

|            | 27.1.1 Operand identifiers and description methods                                                            | 553 |

| heet4U.com | 27.1.2 Description of operation column                                                                        | 554 |

|            | 27.1.3 Description of flag operation column                                                                   | 554 |

|            | 27.2 Operation List                                                                                           | 555 |

|            | 27.3 Instructions Listed by Addressing Type                                                                   | 563 |

| *          | CHAPTER 28 ELECTRICAL SPECIFICATIONS (MASK ROM VERSION)                                                       | 567 |

| *          | CHAPTER 29 ELECTRICAL SPECIFICATIONS (FLASH MEMORY VERSION)                                                   | 597 |

| *          | CHAPTER 30 ELECTRICAL SPECIFICATIONS (FLASH MEMORY VERSION (VDD = 2.5 V))                                     | 627 |

| *          | CHAPTER 31 CHARACTERISTICS CURVES (REFERENCE VALUES)                                                          | 658 |

| *          | CHAPTER 32 PACKAGE DRAWINGS                                                                                   | 660 |

| *          | CHAPTER 33 RECOMMENDED SOLDERING CONDITIONS                                                                   | 662 |

|            | APPENDIX A DIFFERENCES BETWEEN $\mu\text{PD78054}, 78058\text{F}, \text{AND } 780058 \text{ SUBSERIES} \dots$ | 666 |

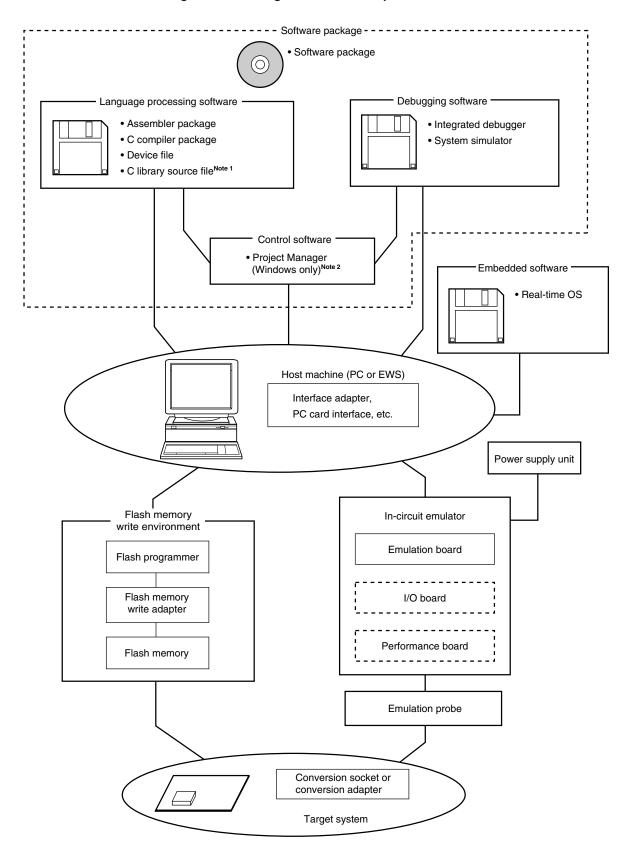

|            | APPENDIX B DEVELOPMENT TOOLS                                                                                  | 668 |

|            | B.1 Software Package                                                                                          | 670 |

|            | B.2 Language Processing Software                                                                              | 670 |

|            | B.3 Control Software                                                                                          | 671 |

|            | B.4 Flash Memory Writing Tools                                                                                | 671 |

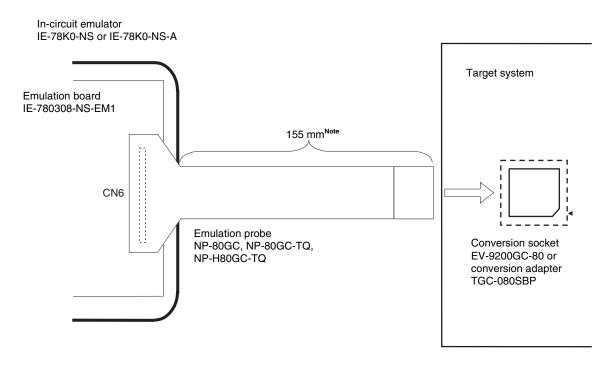

|            | B.5 Debugging Tools (Hardware)                                                                                | 672 |

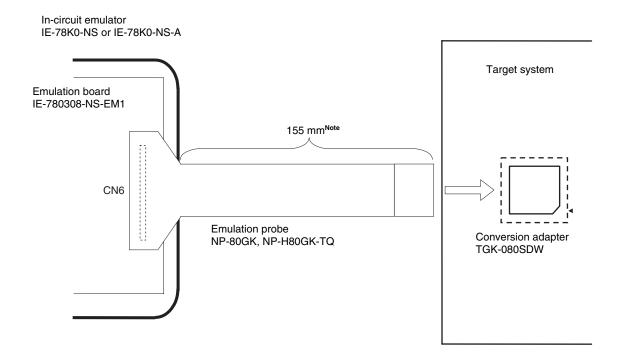

|            | B.5.1 When using in-circuit emulator IE-78K0-NS, IE-78K0-NS-A                                                 | 672 |

|            | B.5.2 When using in-circuit emulator IE-78001-R-A                                                             | 673 |

|            | B.6 Debugging Tools (Software)                                                                                |     |

|            | B.7 Embedded Software                                                                                         | 675 |

|            | B.8 System-Upgrade Method from Former In-Circuit Emulator for 78K/0 Series                                    |     |

|            | to IE-78001-R-A                                                                                               |     |

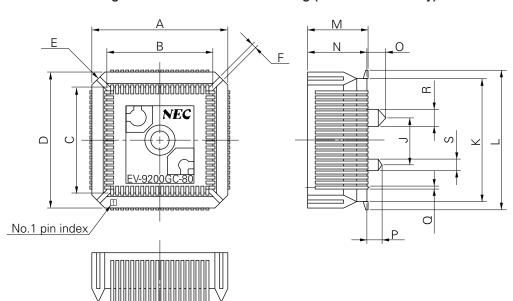

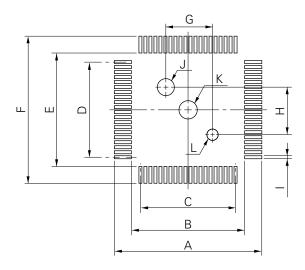

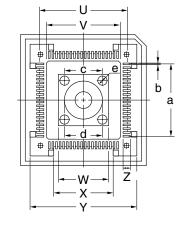

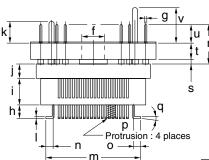

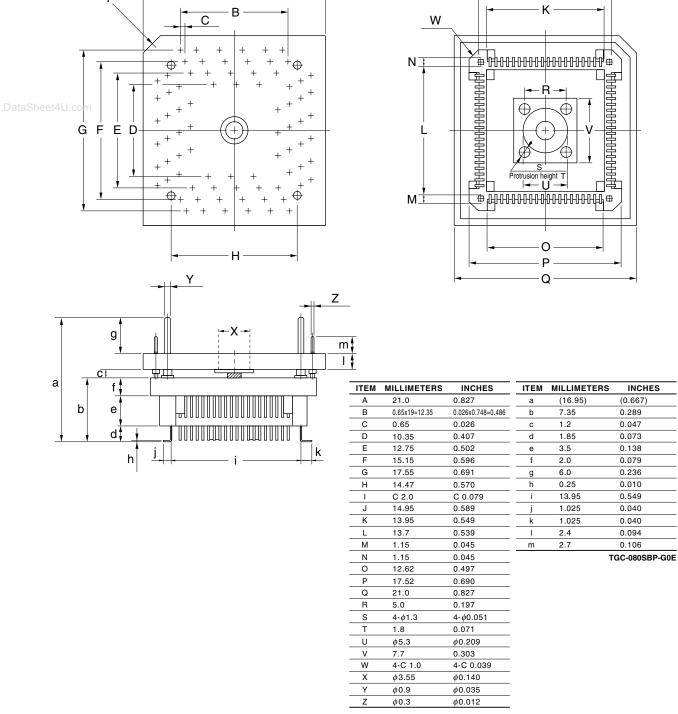

|            | B.9 Drawing and Footprint for Conversion Socket (EV-9200GC-80)                                                |     |

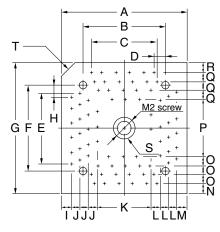

| *          | B.10 Drawing of Conversion Adapter (TGK-080SDW, TGC-080SBP)                                                   | 679 |

| ^          | B.11 Cautions on Designing Target System                                                                      | 681 |

|            | APPENDIX C REGISTER INDEX                                                                                     | 685 |

|            | C.1 Register Index (Register Name)                                                                            | 685 |

|            | C.2 Register Index (Symbol)                                                                                   | 688 |

|            | ADDENDIV D. DEVICION HICTORY                                                                                  |     |

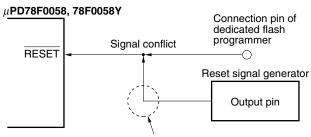

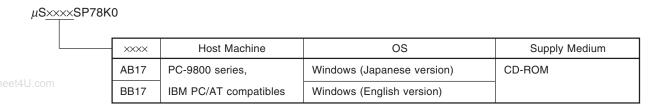

## LIST OF FIGURES (1/8)