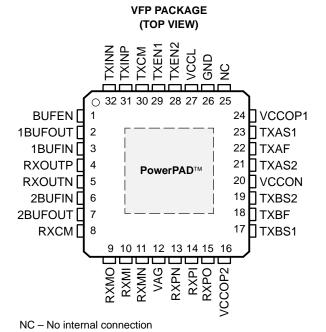

# THS7102 ADSL (POTS) CENTRAL OFFICE LINE INTERFACE DRIVER/RECEIVER

SLOS311B-MAY 2000 - REVISED DECEMBER 2001

- Full Rate ADSL Central Office Line Driver/Receiver for POTS Applications

- 15-V Single Supply Operation

- Low 1.1-W Total Power Consumption

- 0.9-W Transmit Drivers

- 0.2-W Receive Channel

- Active Termination Differential Line Drivers

- No Line Matching Resistors Reduces

Output Voltage and Power Consumption

by up to 50%

- Integrated Differential Receivers

- Includes Analog Filters in Both Transmit and Received Channels

- Multiple Power Saving Modes

- Bias Current Is Adjustable in 20%

Increments to Allow Lower Power Modes for Short Line Lengths

## description

The THS7102 is a low power differential ADSL (POTS) central office line interface driver/receiver. It features active termination drivers that eliminate the matching resistors required with traditional ADSL line drivers. Removal of the matching resistors allows the THS7102 to output nearly half the output voltage as compared with traditional drivers, resulting in power savings of up to 50%. The lower output voltage levels resulting from the active termination also allow the THS7102 to operate on a single 15-V supply, easing power supply requirements.

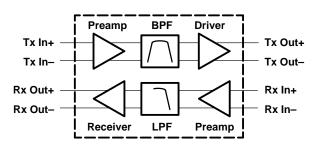

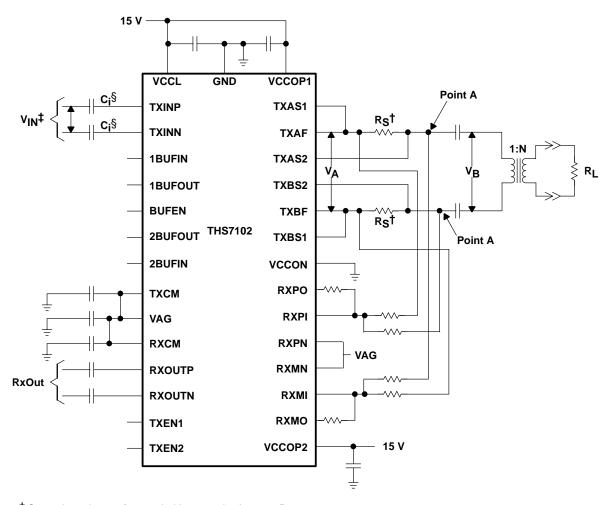

## simplified block diagram

The THS7102 also features integrated differential receivers to reduce the component count on multichannel ADSL line cards. To reduce valuable PCB space further, the transmit path integrates a band-pass filter while the receive path integrates a low-pass filter. Four power-saving modes are featured on this device, allowing it to operate at lower power levels for shorter line lengths.

#### THS7102 Features

| Device  | Application | Transmit<br>Bandpass Filter <sup>†</sup> | Receiver<br>Lowpass Filter |

|---------|-------------|------------------------------------------|----------------------------|

| THS7102 | ADSL (POTS) | 152 kHz to 1.3 MHz                       | 146 kHz                    |

<sup>†</sup> When used in conjunction with the appropriate input capacitor (see the functional block diagram information)

CAUTION: The THS7102 provides ESD protection circuitry. However, permanent damage can still occur if the device is subjected to high-energy electrostatic discharge. Proper ESD precautions are recommended to avoid any performance degradation or loss of functionality.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

TEXAS INSTRUMENTS

POST OFFICE BOX 655303 ● DALLAS, TEXAS 75265

Copyright @ 2001, Texas Instruments Incorporated

#### **AVAILABLE OPTIONS**

| <b>T</b> .    | PACKAGED DEVICES |

|---------------|------------------|

| TA            | PowerPAD (VFP)   |

| 0°C to 70°C   | THS7102CVFP      |

| -40°C to 85°C | THS7102IVFP      |

## absolute maximum ratings over operating free-air temperature (unless otherwise noted)‡

| Supply voltage, VCCL, VCCOP1, VCCOP2 (see Note 1)                                      |                              |

|----------------------------------------------------------------------------------------|------------------------------|

| Input voltage, V <sub>I</sub>                                                          | GND, VCCL, VCCOPx            |

| Output current, IO (see Note 2): Tx outputs                                            | 400 mA                       |

|                                                                                        | 50 mA                        |

| ·                                                                                      | 50 mA                        |

| Differential input voltage, V <sub>ID</sub>                                            |                              |

| ESD rating: HBM                                                                        |                              |

| CDM                                                                                    |                              |

| MM                                                                                     |                              |

| Total power dissipation at (or below) 25°C free-air temperature                        |                              |

| (see Note 2)                                                                           | See Dissipation Rating Table |

| Maximum junction temperature, T <sub>J</sub>                                           |                              |

| Operating free-air temperature, TA: C-suffix                                           |                              |

|                                                                                        | –40°C to 85°C                |

| Storage temperature, T <sub>stq</sub>                                                  |                              |

| Lead temperature 1,6 mm (1/16 in) from case for 10 seconds                             |                              |

| esses beyond those listed under "absolute maximum ratings" may cause permanent da      |                              |

| actional operation of the device at these or any other conditions beyond those indicat |                              |

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 1. VCCL must always be equal to VCCOP1 and VCCOP2

- 2. The THS7102 incorporates a PowerPAD™ on the underside of the chip. This acts as a heatsink and must be connected to a thermally dissipative plane for proper power dissipation. Failure to do so may result in exceeding the maximum junction temperature which could permanently damage the device.

### **DISSIPATION RATING TABLE§**

| PACKAGE | θJA    | (°C/W) | T <sub>A</sub> = 25°C¶ | T <sub>A</sub> = 70°C¶ | T <sub>A</sub> = 85°C¶ |

|---------|--------|--------|------------------------|------------------------|------------------------|

|         | (°C/W) | θJC    | POWER RATING           | POWER RATING           | POWER RATING           |

| VFP     | 29.4   | 0.96   | 3.57 W                 | 2.04 W                 | 1.53 W                 |

<sup>§</sup> This data was taken using 2 oz. trace and copper pad that is soldered directly to a JEDEC standard 4 layer 3 in × 3 in PCB.

The power rating is determined with a junction temperature of 130°C. This is the junction temperature at which distortion begins to substantially increase. Thermal management of the PCB should strive to keep the junction temperature at or below 125°C for the best performance.

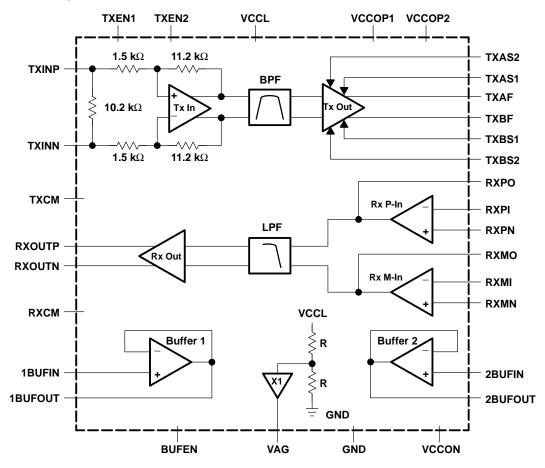

## functional block diagram

The THS7102 is designed to implement full-rate ADSL signals over the same line as POTS signals at the central office (CO). The THS7102 transmit BPF consists of a low-pass filter and a high-pass filter. The low-pass filter portion of the BPF is comprised of a third order Chebyshev filter with a 0.33-dB passband ripple and a breakpoint frequency of 1.3 MHz. The high-pass portion of the BPF is a 0.33-dB passband ripple Chebyshev with a breakpoint frequency at 151.7 kHz. This high-pass section requires that a 680-pF capacitor be used at each transmit input (TXINP and TXINN) for the appropriate Chebyshev response. Together the LPF and HPF form a bandpass filter with a passband ripple of about 0.6 dB. The THS7102 receive LPF is comprised of a fourth order Chebyshev filter with a 0.25-dB passband ripple and a breakpoint frequency of 146 kHz.

#### NOTE:

The definition of breakpoint frequency is the frequency at which the attenuation leaves the ripple band.

# THS7102 ADSL (POTS) CENTRAL OFFICE LINE INTERFACE DRIVER/RECEIVER

SLOS311B- MAY 2000 - REVISED DECEMBER 2001

## **Terminal Functions**

| TERMINAL |        |     | DECODINE                                            |  |  |

|----------|--------|-----|-----------------------------------------------------|--|--|

| NAME     | NO.    | 1/0 | DESCRIPTION                                         |  |  |

| BUFEN    | 1      | I   | Buffer enable – enables buffers 1 and 2             |  |  |

| 1BUFOUT  | 2      | 0   | Buffer 1 output                                     |  |  |

| 1BUFIN   | 3      | I   | Buffer 1 input                                      |  |  |

| 2BUFIN   | 6      | I   | Buffer 2 input                                      |  |  |

| 2BUFOUT  | 7      | 0   | Buffer 2 output                                     |  |  |

| GND      | 26     | I   | Ground                                              |  |  |

| NC       | 25     |     | No connect                                          |  |  |

| RXCM     | 8      | 0   | Receive channel common-mode voltage decoupling node |  |  |

| RXMO     | 9      | 0   | Negative receiver preamp output                     |  |  |

| RXMI     | 10     | I   | Negative receiver preamp inverting input            |  |  |

| RXMN     | 11     | I   | Negative receiver preamp noninverting input         |  |  |

| RXOUTP   | 4      | 0   | Receive channel positive output                     |  |  |

| RXOUTN   | 5      | 0   | Receive channel negative output                     |  |  |

| RXPI     | 14     | I   | Positive receiver preamp inverting input            |  |  |

| RXPN     | 13     | I   | Positive receiver preamp noninverting input         |  |  |

| RXPO     | 15     | 0   | Positive receiver preamp output                     |  |  |

| TXAF     | 22     | 0   | Driver A output                                     |  |  |

| TXBF     | 18     | 0   | Driver B output                                     |  |  |

| TXAS1    | 23     | I   | Driver A sense point 1                              |  |  |

| TXAS2    | 21     | I   | Driver A sense point 2                              |  |  |

| TXBS1    | 17     | I   | Driver B sense point 1                              |  |  |

| TXBS2    | 19     | I   | Driver B sense point 2                              |  |  |

| TXCM     | 30     | 0   | Transmit channel common mode decoupling node        |  |  |

| TXEN1    | 29     | I   | Transmit enable 1                                   |  |  |

| TXEN2    | 28     | I   | Transmit enable 2                                   |  |  |

| TXINN    | 32     | I   | Transmit channel negative input                     |  |  |

| TXINP    | 31     | I   | Transmit channel positive input                     |  |  |

| VAG      | 12     | 0   | Virtual analog ground – is at VCCL/2                |  |  |

| VCCL     | 27     | I   | V <sub>CC</sub> to low level circuitry              |  |  |

| VCCON    | 20     | I   | Output stage negative supply – tie to ground        |  |  |

| VCCOPx   | 16, 24 | I   | Output stage positive V <sub>CC</sub> supply        |  |  |

# recommended operating conditions

|                                               |                      | MIN | NOM | MAX | UNIT |

|-----------------------------------------------|----------------------|-----|-----|-----|------|

| Supply voltage                                | VCCL, VCCOP1, VCCOP2 | 7.5 | 15  | 16  | V    |

| Operating free air temperature T.             | I–suffix             | -40 |     | 85  | °C   |

| perating free-air temperature, T <sub>A</sub> | C-suffix             | 0   |     | 70  | C    |

SLOS311B- MAY 2000 - REVISED DECEMBER 2001

# driver characteristics, VCCL = VCCOPx = 15 V, VCCON = GND, R<sub>S</sub> = 1.35 $\Omega$ , N = 1, R<sub>L</sub> = 27 $\Omega^{\dagger}$ , C<sub>i</sub> = 0.1 $\mu$ F, T<sub>A</sub> = 25°C

|                                 | PARAMETER                                    | TEST CO                     | NDITIONS           | MIN   | TYP   | MAX  | UNIT               |

|---------------------------------|----------------------------------------------|-----------------------------|--------------------|-------|-------|------|--------------------|

| R <sub>IN</sub> -Tx             | Input resistance (single-ended)              |                             |                    | 1.13  | 1.16  | 1.19 | kΩ                 |

| ٧ <sub>A</sub>                  | Output voltage                               | f = 1 MHz,                  | THD ≤ -31 dBc      | 23.8  | 24.4  |      | V <sub>pp</sub>    |

|                                 |                                              | f = 1 MHz                   | 18.9               | 19.2  | 19.5  |      |                    |

| V <sub>A</sub> /V <sub>IN</sub> | Gain (see Note 3 and Figure 1)               | f ≅ 150 kHz (Peak Frequency | uency)             | 22.4  | 22.7  | 23   | dB                 |

| \/ \/ \/                        | Coin (see Note 2 and Figure 4)               | f = 1 MHz                   |                    | 18.1  | 18.4  | 18.7 | 4D                 |

| V <sub>B</sub> /V <sub>IN</sub> | Gain (see Note 3 and Figure 1)               | f ≅ 150 kHz (Peak Frequency | uency)             | 21.6  | 21.9  | 22.2 | dB                 |

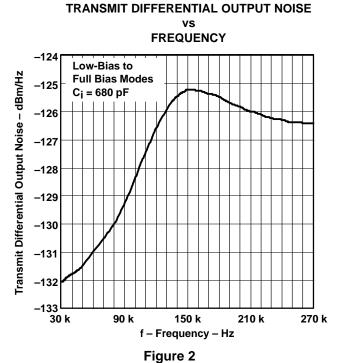

|                                 |                                              | 30 kHz                      |                    |       | 55    |      |                    |

|                                 | Differential output noise                    | 100 kHz                     |                    |       | 85    |      | nV/√ <del>Hz</del> |

|                                 |                                              | 138 kHz                     |                    |       | 118   |      |                    |

| Z <sub>o</sub>                  | Output impedance‡                            | f = 20 kHz to 1.1 MHz       |                    |       | †     |      | Ω                  |

|                                 | Elter comer from success                     | HPF,                        | $C_i = 0.1  \mu F$ | 100   | 107   | 114  | kHz                |

|                                 | Filter corner frequency                      | LPF                         |                    | 1.1   | 1.3   | 1.65 | MHz                |

|                                 | Out of band rejection (relative to the input | $V_O$ at f = 40 kHz         | $C_i = 0.1 \mu F$  | 0     | -2    |      | dB                 |

|                                 | signal)                                      | VO at f = 6 MHz             |                    | -17.5 | -20.5 |      | uБ                 |

|                                 | Channel-to-channel mismatch                  | f = 100 kHz to 800 kHz      |                    | -0.45 | 0     | 0.45 | dB                 |

|                                 | Channel-to-channel mismatch                  | f = 900 kHz to 1.1 MHz      |                    | -0.45 | 0     | 0.5  | ав                 |

|                                 |                                              | Off, $TXEN1 = 0$            | TXEN2 = 0          | 0.7   | 1     | 1.3  |                    |

| laa.                            | Cupply gurrent                               | Low, TXEN1 = 1              | TXEN2 = 0          | 13.1  | 14.6  | 16.1 | mA                 |

| ICCL                            | Supply current                               | Med., TXEN1 = 1             | TXEN2 = 1          | 13.3  | 14.8  | 16.3 | mA                 |

|                                 |                                              | High, TXEN1 = 0             | TXEN2 = 1          | 13.5  | 15    | 16.5 |                    |

|                                 |                                              | Off, $TXEN1 = 0$ ,          | TXEN2 = 0          | 0     | 0.6   | 1.1  |                    |

|                                 |                                              | Low, TXEN1 = 1,             | TXEN2 = 0          | 1.7   | 2.7   | 3.7  | mA                 |

| ICCOP                           | Supply current                               | Med., TXEN1 = 1,            | TXEN2 = 1          | 6     | 7.5   | 9    |                    |

|                                 |                                              | High, $TXEN1 = 0$ ,         | TXEN2 = 1          | 11    | 13    | 15   |                    |

<sup>†</sup> The test circuit of R<sub>S</sub> = 1.35  $\Omega$ , N = 1, and R<sub>L</sub> = 27  $\Omega$  is equivalent to a standard ADSL circuit with R<sub>S</sub> = 1.35  $\Omega$ , N = 1.9, and R<sub>L</sub> = 100  $\Omega$ . ‡ Output impedance is given by Z<sub>0</sub> = 10 × R<sub>S</sub>.

NOTES: 3. Due to the gain of the transmit path, the maximum input voltage should not exceed 3 V<sub>pp</sub> or clipping and distortion occurs.

# receiver characteristics, VCCL = VCCOPx = 15 V, VCCON = GND, R\_S = 1.35 $\Omega$ , N = 1, R\_L = 3.9 k $\Omega$ , R<sub>F</sub> = 5 k $\Omega$ , Gain = 26 dB, T<sub>A</sub> = 25°C

|    | PARAMETER                                                      | TEST CONDITIONS                                    | MIN   | TYP   | MAX | UNIT               |

|----|----------------------------------------------------------------|----------------------------------------------------|-------|-------|-----|--------------------|

| VO | Output voltage                                                 | V <sub>I</sub> = 1 V <sub>pp</sub> , f = 103.5 kHz | 19    | 20    |     | $V_{pp}$           |

|    | Output asias                                                   | At f = 30 kHz                                      |       | 77    |     | ->//s/II=          |

|    | Output noise                                                   | At f = 130 kHz                                     |       | 72    |     | nV/√Hz             |

| Vn | Noise voltage (preamp input noise)                             | f = 20 kHz                                         |       | 2.3   |     | nV/√ <del>Hz</del> |

| In | Noise current (preamp input noise)                             | f = 20 kHz                                         |       | 1.0   |     | pA/√Hz             |

|    | Filter corner frequency                                        | $V_I = 0.5 V_{pp}$                                 | 137.5 | 146.3 | 155 | kHz                |

|    | Out of band rejection (relative to input point A) See Figure 1 | V <sub>O</sub> at f = 400 kHz                      | -11.7 | -13   |     | dB                 |

|    | In-band ripple                                                 | V <sub>O</sub> at f = 55 kHz and 103.5 kHz         |       | 0.2   | 0.5 | dB                 |

|    | Channel-to-channel mismatch                                    | f = 10 kHz to 145 kHz                              | -0.2  | 0     | 0.2 | dB                 |

# THS7102 ADSL (POTS) CENTRAL OFFICE LINE INTERFACE DRIVER/RECEIVER

SLOS311B- MAY 2000 - REVISED DECEMBER 2001

# transmit enable characteristics (TXEN1, TXEN2), VCCL = VCCOPx = 15 V, VCCON = GND, $R_S$ = 1.35 $\Omega$ , N = 1, $T_A$ = 25°C

| BUFEN | TXEN1 | TXEN2 | FUNCTION            | DESCRIPTION                                   |

|-------|-------|-------|---------------------|-----------------------------------------------|

| Х     | 0     | 0     | Tx OFF              | Device completely powered down                |

| Х     | 0     | 1     | Tx ON – 100% bias   | Full power                                    |

| Х     | 1     | 1     | Tx ON – Medium bias | Medium power                                  |

| Х     | 1     | 0     | Tx ON – Low bias    | Low power                                     |

| 0     | Х     | Х     | Buffers off         | Conserves power when buffers are not required |

| 1     | Х     | Х     | Buffers enabled     | Useful for extra RX filtering                 |

NOTE: The default state shall be a logic one (1).

# logic control characteristics, VCCL = VCCOPx = 15 V, VCCON = GND, $R_S$ = 1.35 $\Omega$ , N = 1, $T_A$ = 25°C

|     | PARAMETER              | TEST CONDITIONS          | MIN        | TYP         | MAX | UNIT |

|-----|------------------------|--------------------------|------------|-------------|-----|------|

|     | TXEN1                  | VTXEN1 = 5 V             | <b>-</b> 5 | 0           | 5   |      |

| ΙΗ  | TXEN2                  | V <sub>TXEN2</sub> = 5 V | <b>-</b> 5 | 0           | 5   | μА   |

|     | BUFEN                  | V <sub>BUFEN</sub> = 5 V | -5         | 0           | 5   |      |

|     | TXEN1                  | VTXEN1 = 0 V             | -70        | -50         | -30 |      |

| ЦL  | TXEN2                  | V <sub>TXEN2</sub> = 0 V | -70        | <b>-</b> 55 | -30 | μΑ   |

|     | BUFEN                  | V <sub>BUFEN</sub> = 0 V | -70        | -50         | -30 |      |

| VIH | All logic control pins |                          |            | ≥2.3        |     | V    |

| VIL | All logic control pins |                          |            | ≤0.8        |     | V    |

# miscellaneous characteristics, VCCL = VCCOPx = 15 V, VCCON = GND, $R_S$ = 1.35 $\Omega$ , N = 1, $T_A$ = 25°C

|    | PARAMETER              | TEST CONDITIONS        | MIN | TYP | MAX | UNIT |

|----|------------------------|------------------------|-----|-----|-----|------|

| ٧o | Output voltage, VAG    |                        | 7.4 | 7.5 | 7.6 | V    |

| VO | Output voltage, buffer | V <sub>I</sub> = 7.5 V | 7.0 | 7.5 | 8.0 | V    |

### **TYPICAL CHARACTERISTICS**

## TRANSMIT DIFFERENTIAL OUTPUT NOISE **FREQUENCY** 130 Low-Bias to Transmit Differential Output Noise -nV/√Hz **Full Bias Modes** 120 $C_{i} = 680 pF$ 110 100 90 80 70 60 50 90 k 150 k 210 k 30 k 270 k f - Frequency - Hz

Figure 1

### **APPLICATION INFORMATION**

<sup>&</sup>lt;sup>†</sup> Output impedance of transmit driver at point A =  $10 \times R_S$

Figure 3. Typical THS7102 Circuit Configuration

<sup>\$\\$\\$</sup>Maximum input of  $V_{IN} = 3 V_{pp}$ .

<sup>§</sup> In ADSL systems, it is recommended to use  $C_i$  = 680 pF for the THS7102. For testing purposes, use  $C_i$  = 0.1  $\mu$ F

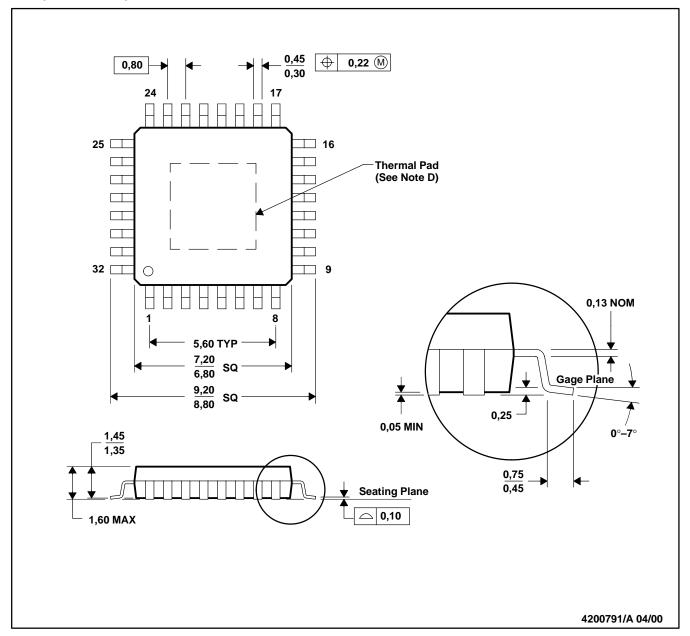

### **MECHANICAL DATA**

### VFP (S-PQFP-G32)

### PowerPAD™ PLASTIC QUAD FLATPACK

- NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

- D. The package thermal performance may be enhanced by bonding the thermal pad to an external thermal plane. This pad is electrically and thermally connected to the backside of the die and possibly selected leads.

- E. Falls within JEDEC MS-026

PowerPAD is a trademark of Texas Instruments.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265