# **DATASHEET**

0.11 μm Processor System for ARM926EJ-S™

cw001200\_agflxr\_2\_0

February 2005

Preliminary

This document is preliminary. As such, it contains data derived from functional simulations and performance estimates. LSI Logic has not verified either the functional descriptions, or the electrical and mechanical specifications using production parts.

This document contains proprietary information of LSI Logic Corporation. The information contained herein is not to be used by or disclosed to third parties without the express written permission of an officer of LSI Logic Corporation.

Purchase of I<sup>2</sup>C components of LSI Logic Corporation, or one of its sublicensed Associated Companies, conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C standard Specification as defined by Philips.

Document DB08-000261-01, February 2005

This document describes LSI Logic Corporation's 0.11  $\mu$ m Processor System for ARM926EJ-S cw001200\_agflxr\_2\_0 and will remain the official reference source for all revisions/releases of this product until rescinded by an update.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 2004, 2005 by LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

LSI Logic, the LSI Logic logo design, CoreWare, Gflx, GigaBlaze, HyperPHY, RapidChip, RapidReady, and RapidWorx are trademarks or registered trademarks of LSI Logic Corporation. ARM and Multi-ICE are registered trademarks and ARM926EJ-S and EmbeddedICE are trademarks of ARM Ltd., used under license. All other brand and product names may be trademarks of their respective companies.

**JSS**

To receive product literature, visit us at <a href="http://www.rapidchip.com">http://www.rapidchip.com</a>.

For a current list of our distributors, sales offices, and design resource centers, view our web page located at

http://www.lsilogic.com/contacts/index.html

## **Preface**

The 0.11  $\mu$ m Processor System for ARM926EJ-S<sup>TM</sup> (cw001200\_agflxr\_2\_0) is compatible with the RapidWorx<sup>®</sup> design tools and design methodology and based on 0.11  $\mu$ m process technology.

#### **Audience**

This document is intended for software engineers, hardware engineers, system architects, platform ASIC designers, engineering managers, and marketing managers who are evaluating the Processor System for ARM926EJ-S.

This document assumes that you have some familiarity with microprocessors and related support devices. The people who benefit from this book are:

- Engineers and managers who are evaluating the processor for possible use in a system

- Engineers who are designing the processor into a system

#### Organization

This document contains the following chapters:

- Chapter 1, Introduction, defines the RapidChip<sup>®</sup> system, introduces its main CoreWare components, and provides an overview of RapidChip Platform ASIC, CoreWare IP, and the Processor System for ARM926EJ-S.

- Chapter 2, **Architectural Description**, describes the Processor System for ARM926EJ-S architecture.

- Chapter 3, Registers, describes the Processor System for ARM926EJ-S programming model.

- Chapter 4, Signal Summary, describes the signals used by the Processor System for ARM926EJ-S.

- Chapter 5, Specifications, describes the specifications required by the Processor System for ARM926EJ-S.

#### **Related Publications**

The following LSI Logic publications are related to this document:

- 0.11 μm Processor System for ARM926EJ-S Technical Manual, DB14-000299-01

- 0.11 μm Processor System for ARM926EJ-S Integration Guide, DB09-000147-02

- 0.11 μm Processor System for ARM926EJ-S Release Notes

- 0.11 μm Processor System for ARM926EJ-S Errata

#### Conventions Used in This Manual

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive. Signals that are active LOW end in an "n."

Hexadecimal numbers are indicated by the prefix "0x"—for example, 0x32CF. Binary numbers are indicated by the prefix "0b"—for example, 0b0011.0010.1100.1111.

# **Contents**

| Chapter 1<br>Introduction |         |                                                     |     |

|---------------------------|---------|-----------------------------------------------------|-----|

|                           | 1.1     | RapidChip Technology Overview                       | 1-1 |

|                           |         | 1.1.1 RapidChip Platform ASICs                      | 1-1 |

|                           |         | 1.1.2 CoreWare IP Program                           | 1-2 |

|                           |         | 1.1.3 RapidReady™ Certification                     | 1-2 |

|                           |         | 1.1.4 RapidWorx                                     | 1-2 |

|                           | 1.2     | Processor System for ARM926EJ-S Product Description | 1-3 |

|                           |         | 1.2.1 Processor System for ARM926EJ-S Overview      | 1-3 |

|                           |         | 1.2.2 Processor System for ARM926EJ-S Features and  |     |

|                           |         | Benefits                                            | 1-4 |

|                           |         | 1.2.3 Processor System for ARM926EJ-S Options       | 1-5 |

|                           |         | 1.2.4 Processor System for ARM926EJ-S Deliverables  | 1-6 |

|                           | 1.3     | Required Platform ASIC Resources                    | 1-6 |

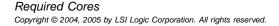

|                           | 1.4     | Required Cores                                      | 1-7 |

|                           | <u></u> |                                                     |     |

| Chapter 2                 |         |                                                     |     |

| Architectural Des         | criptio | o <mark>n</mark>                                    |     |

|                           | 2.1     | Processor System for ARM926EJ-S Block Diagram       | 2-1 |

|                           | 2.2     | ARM926EJ-S Processor Block Description              | 2-2 |

|                           | 2.3     | Instruction AHB Bus Block Description               | 2-3 |

|                           | 2.4     | Data AHB Bus Block Description                      | 2-3 |

|                           | 2.5     | APB Bus Block Description                           | 2-4 |

|                           | 2.6     | Interrupts                                          | 2-5 |

| (A)                       |         |                                                     |     |

| Chapter 3<br>Registers    |         |                                                     |     |

| 10                        | 3.1     | Register Summary                                    | 3-1 |

|                           |         | 3.1.1 External SRAM Registers                       | 3-1 |

|                           |         |                                                     |     |

|                             |     | 3.1.2    | GPIO Registers                | 3-1  |

|-----------------------------|-----|----------|-------------------------------|------|

|                             |     | 3.1.3    | UART Registers                | 3-3  |

|                             |     | 3.1.4    | APB Timer Registers           | 3-4  |

|                             |     | 3.1.5    | Ethernet Controller Registers | 3-4  |

|                             |     | 3.1.6    | ApI2c Registers               | 3-6  |

|                             |     | 3.1.7    | ApVic Registers               | 3-9  |

|                             |     | 3.1.8    | Remap Register                | 3-10 |

|                             | 3.2 | Systen   | n Memory Map                  | 3-10 |

|                             |     | 3.2.1    | System Boot Settings          | 3-10 |

|                             |     | 3.2.2    | Memory Map and Addressing     | 3-11 |

| Chapter 4<br>Signal Summary |     |          |                               |      |

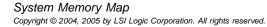

|                             | 4.1 | Systen   | n Interfaces                  | 4-1  |

|                             | 4.2 | Interfac | ce Signals                    | 4-4  |

| Chapter 5                   |     |          |                               |      |

| Specifications              |     |          |                               |      |

|                             | 5.1 |          | al Specifications             | 5-1  |

|                             | 5.2 | Operat   | ting Conditions               | 5-1  |

|                             | 5.3 | AC Ele   | ectrical Specifications       | 5-2  |

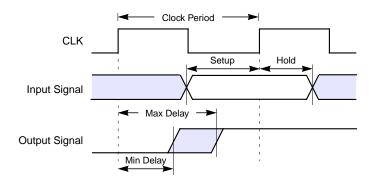

|                             |     | 5.3.1    | Input Timing                  | 5-3  |

|                             |     | 5.3.2    | Output Timing                 | 5-7  |

|                             |     | 5.3.3    | Pass-Through Timing           | 5-12 |

| Figures |     |                                               |     |

|---------|-----|-----------------------------------------------|-----|

|         | 2.1 | Processor System for ARM926EJ-S Block Diagram | 2-2 |

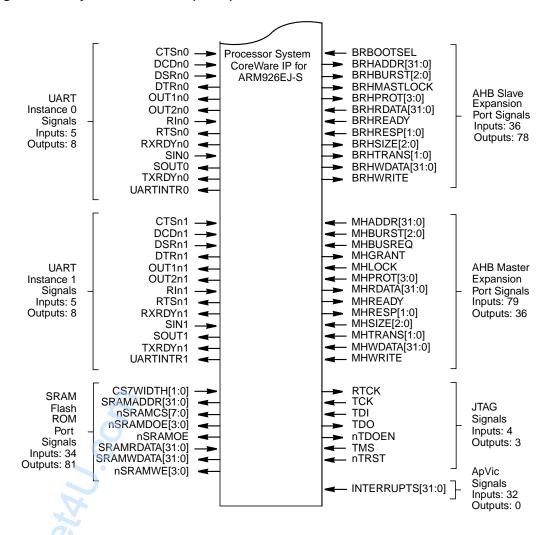

|         | 4.1 | System Interfaces                             | 4-2 |

|         | 5.1 | AC Specifications                             | 5-2 |

#### **Tables**

| 3.1  | Chip Select Control Register Summary                     | 3-1  |

|------|----------------------------------------------------------|------|

| 3.2  | GPIO Register Summary                                    | 3-2  |

| 3.3  | UART Register Summary                                    | 3-3  |

| 3.4  | APB Timer Register Summary                               | 3-4  |

| 3.5  | Ethernet Controller Register Summary                     | 3-4  |

| 3.6  | ApI2c Register Summary                                   | 3-7  |

| 3.7  | ApVic Register Summary                                   | 3-9  |

| 3.8  | Chip Select Control Register Summary                     | 3-10 |

| 3.9  | System Boot Setting: BRBOOTSEL=0                         | 3-11 |

| 3.10 | System Boot Setting: BRBOOTSEL=1                         | 3-11 |

| 3.11 | Address Map for Instruction AHB Bus—TCMs Disabled        | 3-12 |

| 3.12 | Address Map for Instruction AHB Bus—TCMs Enabled         | 3-13 |

| 3.13 | Address Map for Data AHB Bus—TCMs Disabled               | 3-14 |

| 3.14 | Address Map for Data AHB Bus—TCMs Enabled                | 3-15 |

| 3.15 | Address Map for APB Bus Peripherals (TCMs Enabled or     |      |

|      | Disabled)                                                | 3-16 |

| 4.1  | Clock Generation Signals                                 | 4-4  |

| 4.2  | Reset Signals                                            | 4-5  |

| 4.3  | ARM926EJ-S Signals                                       | 4-5  |

| 4.4  | AHB Master Expansion Port Signals                        | 4-6  |

| 4.5  | Ethernet Signals                                         | 4-6  |

| 4.6  | ApVic Signals                                            | 4-8  |

| 4.7  | Apl2c Signals                                            | 4-8  |

| 4.8  | UART Signals                                             | 4-9  |

| 4.9  | GPIO Signals                                             | 4-10 |

| 4.10 | Timer Signals                                            | 4-10 |

| 4.11 | SRAM, Flash, ROM Port Signals                            | 4-10 |

| 4.12 | Instruction AHB Multiport Memory Controller Port Signals | 4-11 |

| 4.13 | Data AHB Multiport Memory Controller Port Signals        | 4-11 |

| 4.14 | AHB Slave Expansion Port Signals                         | 4-12 |

| 4.15 | JTAG Signals                                             | 4-13 |

| 5.1  | Processor System for ARM926EJ-S Timing Conditions        | 5-2  |

| 5.2  | Maximum Clock Frequency                                  | 5-3  |

| 5.3  | Input Timing in the CLK Domain                           | 5-4  |

| 5.4  | Input Timing in the HCLK Domain                          | 5-4  |

| 5.5  | Input Timing in the HOST CLK Domain                      | 5-5  |

| 5.6  | Input Timing in the MII_RXCLK Domain  | 5-6  |

|------|---------------------------------------|------|

| 5.7  | Input Timing in the MII_TXCLK Domain  | 5-6  |

| 5.8  | Input Timing in the PCLK Domain       | 5-6  |

| 5.9  | Input Timing in the TCK Domain        | 5-7  |

| 5.10 | Output Timing in the CLK Domain       | 5-8  |

| 5.11 | Output Timing in the HCLK Domain      | 5-8  |

| 5.12 | Output Timing in the HOST_CLK Domain  | 5-10 |

| 5.13 | Output Timing in the MII_RXCLK Domain | 5-10 |

| 5.14 | Output Timing in the MI_TXCLK Domain  | 5-11 |

| 5.15 | Output Timing in the PCLK Domain      | 5-11 |

| 5.16 | Pass-Through Paths in the HCLK Domain | 5-13 |

# Chapter 1 Introduction

The 0.11  $\mu m$  Processor System for ARM926EJ-S<sup>TM</sup> is compatible with the RapidWorx<sup>®</sup> design tools and design methodology and ready to integrate into the RapidChip<sup>®</sup> Platform ASIC families.

This chapter contains the following sections:

- Section 1.1, "RapidChip Technology Overview"

- Section 1.2, "Processor System for ARM926EJ-S Product Description"

#### 1.1 RapidChip Technology Overview

RapidChip Platform ASICs, RapidWorx design methodology, and RapidWorx design tools are all based on RapidChip Technology. This section briefly explains these concepts. For more information about RapidChip Technology, go to <a href="http://www.rapidchip.com">http://www.rapidchip.com</a>.

#### 1.1.1 RapidChip Platform ASICs

RapidChip Technology allows you to customize the metal layers of a partially manufactured semiconductor wafer that contains multiple copies of a predefined platform ASIC. The silicon layers of a platform ASIC have diffused IP resources that are later connected with user-specific metallization patterns.

Because platform ASICs are available as partially manufactured devices, customers benefit from dramatically reduced lead times for prototypes and production units as well as lower inventory costs. The broad range of resources available in platform ASICs meets the needs of many different systems and applications.

Each platform ASIC incorporates diffused memory blocks, PLLs, and IP blocks from our extensive CoreWare<sup>®</sup> library. In addition, each platform ASIC has a transistor fabric region and an I/O ring, which are both user-configurable.

#### 1.1.2 CoreWare IP Program

The LSI Logic CoreWare IP library provides the industry's most comprehensive set of IP solutions that work seamlessly in the cell-based ASIC design flow and the RapidWorx Design Kit. Customers can leverage CoreWare IP solutions to significantly reduce the risk and turn-around times associated with complex System on a Chip (SoC) designs. CoreWare IP includes:

- GigaBlaze<sup>®</sup> and HyperPHY<sup>®</sup> high-speed, standards-compliant SerDes

- High-performance ARM<sup>®</sup> and MIPS processors and associated systems and reference designs

- Processor peripherals and AMBA on-chip-bus structures

- DSP cores

- USB cores

- Memory PHYs and controllers

- Ethernet MAC and PHY cores

- PCI Express, XGXS, SPI4.2, and other protocol layer IP

#### 1.1.3 RapidReady™ Certification

CoreWare IP can have RapidReady certification, which means it meets the highest level of compatibility with the RapidWorx design methodology and design tools and is ready to be integrated into RapidChip Platform ASICs. For more information about RapidReady certification refer to <a href="http://www.rapidchip.com">http://www.rapidchip.com</a>.

#### 1.1.4 RapidWorx

The RapidWorx design tools and design methodology are used to customize a RapidChip Platform ASIC, creating a unique metallized device, called an *instance*.

RapidWorx design tools help you create design structures for implementing a custom IC design. Based on user inputs, these tools automatically generate clock, memory, test, and I/O structures, relieving the design team of more mundane design tasks. This dramatically reduces the overall manpower resource required to design custom high-performance ICs. Additionally, these structures are "correct by construction" and optimized to ensure ease of implementation during the physical design phase.

RapidWorx design methodology is compatible with best-in-class thirdparty EDA tools. Rules and constraints guide designers throughout the design process to ensure predictable results and reduced design times when compared to fully optimized ASICs.

#### 1.2 Processor System for ARM926EJ-S Product Description

This section provides an overview of the Processor System for ARM926EJ-S, including its features and benefits, product options, and product deliverables.

#### 1.2.1 Processor System for ARM926EJ-S Overview

The 0.11 μm Processor System for ARM926EJ-S is a general purpose microprocessor typically used in the following applications:

- Portable communications

- Hand-held computing

- Multimedia

- Digital consumer

- Embedded solutions

| Product Name                           | 0.11 μm Processor System for ARM926EJ-S |  |

|----------------------------------------|-----------------------------------------|--|

| CoreWare IP Number cw001200_agflxr_2_0 |                                         |  |

| Process Technology                     | 0.11 Micron                             |  |

| IP Type                                | Firm IP                                 |  |

| Library                                | Gflx™-r                                 |  |

#### 1.2.2 Processor System for ARM926EJ-S Features and Benefits

The Processor System for ARM926EJ-S offers the following features and benefits:

- ARM926EJ-S processor

- Two AHB slave ports for connecting a multiport memory controller or other AHB slave to the ARM926EJ-S 32-bit instruction and data buses

- APB peripheral set: UARTs, GPIO, timers, and I<sup>2</sup>C bus controllers.

- Industry standard AMBA 2.0 Bus family

- Advanced High-Performance Bus (AHB)

- Advanced Peripheral Bus (APB)

- Supports little endian systems only

- JTAG debug port

- Clocking system supports integer-multiple bus frequencies for AHB and APB buses

- External SRAM, flash, and ROM memory controller

- 32-bit external data bus

- 32-bit external address bus

- Assembles and disassembles 8-bit, 16-bit, and 32-bit AHB requests to external 8-bit, 16-bit, and 32-bit devices

- Programmable wait state control (1–16) that supports external flash memory

- AHB Arbiter

- Vectored Interrupt Controller (ApVic)

- I-AHB and D-AHB can access external SRAM, flash, and ROM memory controller

- 10/100 Mbit/s Ethernet Controller (ApE110) with AMBA Master DMA interface

- 32-bit AHB Master Expansion Port

- I-AHB and D-AHB can access 32-bit AHB to AHB synchronous Segmentation Bridge for external AHB slaves

#### 1.2.3 Processor System for ARM926EJ-S Options

Configuration options for the Processor System for ARM926EJ-S are as follows:

Compile-Time Options

The Processor System for ARM926EJ-S has no compile time options.

Programmable Options

Programmable options are customer selectable options. The programmable options are peripheral dependent and are captured by the peripheral register section.

Strappable Options

Strap pins are options available at the system boundary. These strappable pins must be held HIGH or LOW to enable or disable the particular feature. The following table lists the options.

| Interface      | Signal          | Strapping                                                                                           |

|----------------|-----------------|-----------------------------------------------------------------------------------------------------|

| Decoding Logic | BRBOOTSEL       | LOW: Processor boots from SRAM, Flash, ROM port HIGH: Processor boots from AHB Slave Expansion Port |

| ApE110         | CLKS            | Clock Select pin                                                                                    |

| ApSramCtlr     | CS7WIDTH        | Chip Select 7 Data Select Width defines the data path width                                         |

| ARM926EJ-S     | DRSIZE          | Data TCM size; set internally by TCM configuration process                                          |

| ApE110         | E110RX_RAM_SIZE | Receive FIFO RAM size                                                                               |

| ApE110         | E110TX_RAM_SIZE | Transmit FIFO RAM size                                                                              |

| ARM926EJ-S     | INITRAM         | Enables Instruction TCM at reset                                                                    |

| ARM926EJ-S     | IRSIZE          | Instruction TCM size; set internally by TCM configuration process                                   |

| ARM926EJ-S     | VINITHI         | LOW: Exception vectors start at 0x00000000<br>HIGH: Exception vectors start at 0xFFFF0000           |

#### 1.2.4 Processor System for ARM926EJ-S Deliverables

Typical Firm IP Deliverables:

| Deliverable                                                                                                                        | Yes/No |

|------------------------------------------------------------------------------------------------------------------------------------|--------|

| Encrypted or Behavioral Verilog to support the following simulators: Mentor Graphics Modelsim, Cadence NCVerilog, and Synopsys VCS | Yes    |

| Verilog gate level netlist                                                                                                         | Yes    |

| Verilog test wrapper to support automated test insertion flow                                                                      | Yes    |

| Abstracted Timing (estimated) and LEF models to support chip level RTL analysis                                                    | Yes    |

| Timing constraints for synthesis and physical layout                                                                               | Yes    |

| RapidWorx data files                                                                                                               | Yes    |

| Simulation testbench, run control scripts, and test stimuli                                                                        | Yes    |

| Datasheet                                                                                                                          | Yes    |

| Technical Manual                                                                                                                   | Yes    |

| Integration Guide                                                                                                                  | Yes    |

| Release Notes                                                                                                                      | Yes    |

| Errata                                                                                                                             | Yes    |

# 1.3 Required Platform ASIC Resources

This Processor System for ARM926EJ-S requires the ARM926EJ-S processor identified below:

| Compatible CoreWare IP | Description                    | Format      |

|------------------------|--------------------------------|-------------|

| cw001124_1_0           | ARM926EJ-S processor, rev r0p4 | Hard R-Cell |

The table below identifies the platform ASIC resources for the Processor System for ARM926EJ-S:

| Resource    | Description                                                                                                                                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory      | Ethernet memories are external to the cw001200; you can choose the memory size using strap pin settings and how to implement the memory (R-Cell, diffused memory in slice, and so on) |

| R-Cells     | Requires the ARM926EJ-S processor core                                                                                                                                                |

| I/O Buffers | No special I/O requirements, however some signals (SRAM, GPIO, UART, I <sup>2</sup> C, and so on) require them                                                                        |

| PLLs        | No special PLL requirement other than you must generate the CLK, HCLK, PCLK, HOST_CLK, and so on                                                                                      |

# 1.4 Required Cores

The following table identifies the physical requirements of the Processor System for ARM926EJ-S:

| Requirement            | Description                                                                                                                                                                                                                                                                                              |  |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Type (Firm)            | Encrypted RTL     Test ready netlist                                                                                                                                                                                                                                                                     |  |  |

| Memory<br>Requirements | <ul> <li>Data TCM—Single Port SRAM, size determined by customer</li> <li>Instruction TCM—Single Port SRAM, size determined by customer</li> <li>Ethernet Receive FIFO—Dual Port SRAM, size determined by customer</li> <li>Ethernet Transmit FIFO—Dual Port SRAM, size determined by customer</li> </ul> |  |  |

| Clocks Required        | Six clocks required     Up to three clock enables depending on clock frequencies                                                                                                                                                                                                                         |  |  |

| Reset Scheme           | <ul><li>Asynchronous with de-assertion synchronous</li><li>Three resets required</li></ul>                                                                                                                                                                                                               |  |  |

# Chapter 2 Architectural Description

The 0.11  $\mu$ m Processor System for ARM926EJ-S, part of the CoreWare IP library, easily integrates with the RapidChip Platform ASIC design flow. This fully integrated, general purpose system is built from existing LSI Logic CoreWare IP blocks and delivered as a Fixed IP block. Expansion ports let you add external features and application-specific hardware to the subsystem.

This chapter contains the following sections:

- Section 2.1, "Processor System for ARM926EJ-S Block Diagram"

- Section 2.2, "ARM926EJ-S Processor Block Description"

- Section 2.3, "Instruction AHB Bus Block Description"

- Section 2.4, "Data AHB Bus Block Description"

- Section 2.5, "APB Bus Block Description"

- Section 2.6, "Interrupts"

### 2.1 Processor System for ARM926EJ-S Block Diagram

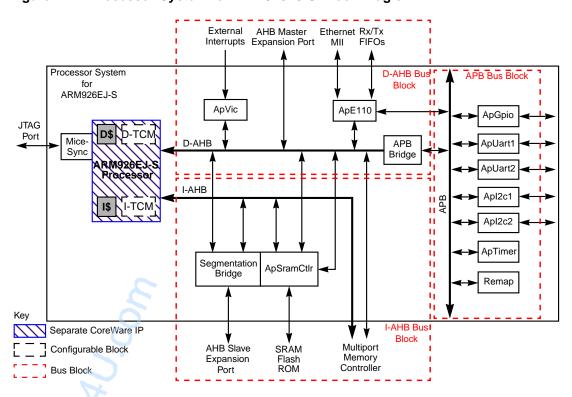

The Processor System for ARM926EJ-S is intended as the primary processor in a larger AMBA system. Other system processors are expected to be Slaves for startup and system control functions.

Because the Processor System for ARM926EJ-S serves as the main communication protocol control processor for a larger AMBA system, the Processor System for ARM926EJ-S includes a 10/100 Ethernet Controller (ApE110). Additional IP blocks, such as USB interfaces and PCI interfaces, can be added to the system using the AHB Slave Expansion Port, the AHB Master Expansion Port, and the Multiport Memory Controller ports.

The processor system includes an ARM926EJ-S microprocessor and commonly required system peripherals, such as timers, UARTs, a vectored interrupt controller, an Ethernet controller, and controllers for SRAM, flash, and ROM memories.

Figure 2.1 shows the Processor System for ARM926EJ-S block diagram.

Figure 2.1 Processor System for ARM926EJ-S Block Diagram

#### 2.2 ARM926EJ-S Processor Block Description

The ARM926EJ-S processor is a separate CoreWare IP component. This block consists of the ARM926EJ-S soft macro, memories to create the data and instruction tightly coupled memories (TCMs), if supported by the Processor System for ARM926EJ-S component, and the processor.

#### 2.3 Instruction AHB Bus Block Description

The instruction AHB bus is based on the AMBA 2.0 AHB standard from ARM Ltd. This ARM926EJ-S AHB Master bus includes the following Slave devices:

- External SRAM Controller (ApSramCtlr)

- AHB-lite port to an external Multiport Memory Controller

- Segmentation Bridge to an expansion AHB-lite bus

The Bus Matrix boots the subsystem from either the External SRAM Controller or Segmentation Bridge which are aliased at both 0x0 and 0xF000.0000. The boot device is controlled by the BTBOOTSEL strap pin. Booting HIGH or LOW is controlled by the VINITHI strap pin.

The AHB-lite port lets you connect to a memory controller, for example the LSI Logic DDR SDRAM controller.

#### 2.4 Data AHB Bus Block Description

The data AHB bus is based on the AMBA 2.0 AHB standard from ARM Ltd. This AHB bus has three masters:

- 10/100 Mbit/s Ethernet Controller (ApE110)

- ARM926EJ-S Processor

- Expansion Master Port

The three masters are controlled by a priority arbiter. The highest priority master is the Ethernet controller (ApE110), the intermediate level master is the ARM926EJ-S, and the lowest priority master is the Expansion Master Port.

The Expansion Master Port is an AHB port to allow an external Master access to peripherals on the data AHB bus. This port lets you add additional IP to the system.

The data AHB bus has the following Slave devices:

- External SRAM Controller (ApSramCtlr)

- AHB-lite port to an external Multiport Memory Controller

- Vectored Interrupt Controller (ApVic and ApVicBridge)

- APB Bridge

- Segmentation Bridge to an expansion AHB-lite bus

The Expansion Master Port, AHB expansion bus port, and the AHB-lite port, for an external Multiport Memory Controller, lets you add additional IP to the system. The AHB-lite port is provided to allow connection to memory controller, such as the LSI Logic DDR SDRAM controller.

The APB bridge allows all data AHB Masters to access peripherals on the APB bus.

#### 2.5 APB Bus Block Description

The APB is a Slave bus based on the AMBA 2.0 APB standard from ARM Ltd. The APB includes the following peripherals:

- Two UART (16550 type) instantiations

- A 32-bit GPIO block

- Two I<sup>2</sup>C Bus Controller instantiations

- Timer block (two timers)

- Ethernet Controller Configuration port

- Remap block

#### 2.6 Interrupts

The 32-bit input interrupt channel to the Vectored Interrupt Controller, ApVic, is brought to the top interface of the system as an input. You must connect the peripheral interrupt outputs to the appropriate ApVic interrupt channels. There are no interrupts connected to the ApVic internally.

Interrupts for all the instantiated system peripherals are brought to the top interface of the system as outputs. These include:

- One interrupt for the Ethernet Controller

- One interrupt for each I<sup>2</sup>C instantiation

- One interrupt for each UART instantiation

- Six interrupts for the Timer block

- Four interrupts for the GPIO block

2-5

# Chapter 3 Registers

This chapter summarizes the Processor System for ARM926EJ-S registers.

This chapter contains the following sections:

- Section 3.1, "Register Summary"

- Section 3.2, "System Memory Map"

# 3.1 Register Summary

This section summarizes the system registers.

#### 3.1.1 External SRAM Registers

Eight Chip Select Control registers control the AHB address chip select decoding. Chip Select 7 has the highest priority, Chip Select 0 the lowest.

The registers are accessed through the AHB from the D-AHB bus.

The peripheral register set consists of the registers summarized in Table 3.1.

Table 3.1 Chip Select Control Register Summary

| Register Name                                | R/W | Function                                             |

|----------------------------------------------|-----|------------------------------------------------------|

| Chip Select Control Register 0/1/2/3/4/5/6/7 | R/W | Controls the chip select decoding of the AHB address |

#### 3.1.2 GPIO Registers

The GPIO registers set the external GPIO bits for use as General-Purpose Input/Output. Each GPIO bit can be configured as an

input or output through the Direction register. The GPIO also can generate interrupts to the processor's FIQ/IRQ interrupt system.

Each register set defines a particular behavior for all of the external GPIO pins. There is one bit for each GPIO pin. This definition is the same for all register sets. For example:

- GPIO Data Direction Register 1, bit 7 controls the direction for external GPIO bit 7.

- GPIO Data Direction Register 1, bit 0 controls the direction for external GPIO bit 0.

- GPIO Data Direction Register 2, bit 7 controls the direction for external GPIO bit 15.

- GPIO Data Direction Register 2, bit 0 controls the direction for external GPIO bit 8.

The GPIO register set is summarized in Table 3.2.

Table 3.2 GPIO Register Summary

| Register Name               | R/W | Function                                                                                                                                       |  |

|-----------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GPIO Data Direction 1/2/3/4 | R/W | Sets the direction of the corresponding GPIO bits                                                                                              |  |

| GPIO Data In 1/2/3/4        | R   | Reads the data value for the corresponding GPIO bit                                                                                            |  |

| GPIO Data Out 1/2/3/4       | W   | Writes the data value for the corresponding GPIO bit                                                                                           |  |

| GPIO Edge 1/2/3/4           | R/W | Selects whether an edge or level signal on the GPIO generates an interrupt                                                                     |  |

| GPIO Enable Clear 1/2/3/4   | R/W | Clears the enables for the GPIO interrupts                                                                                                     |  |

| GPIO Enable Set 1/2/3/4     | R/W | Sets the enables for the GPIO interrupts                                                                                                       |  |

| GPIO Polarity 1/2/3/4       | R/W | Selects whether the GPIO interrupt is active HIGH or LO (edge bit = level), or, if edge triggered (edge bit = edge), or falling or rising edge |  |

| GPIO Raw Status 1/2/3/4     | R/W | Reads the raw (premasked) interrupt status of the GPIO interrupts; on writes, a 1 in a bit position clears the corresponding interrupt bit     |  |

| GPIO Resync 1/2/3/4         | R/W | Selects whether the GPIO inputs are resynchronized to the internal clock when configured as an input                                           |  |

| GPIO Status 1/2/3/4         | R   | Reads the (postmasked) interrupt status of the GPIO interrupts                                                                                 |  |

#### 3.1.3 UART Registers

The registers are accessed through the APB. The Divisor Latch Access Bit (DLAB) is set and cleared by writing to bit 7 of the Line Control Register (LCR).

The UART register set consists of 17 registers, summarized in Table 3.3.

Table 3.3 UART Register Summary

| Register Name                                     | R/W | Description                                                                                                                        |  |

|---------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------|--|

| Divisor Latch Low/High (DLL/DLH)                  | R/W | Stores the divisor for a baud generator in a 16-bit binary format                                                                  |  |

| FIFO Control (FCR)                                | W   | Provides control for both the receive and transmit FIFOs                                                                           |  |

| Interrupt Enable (IER)                            | R/W | Enables the five types of UART interrupts                                                                                          |  |

| Interrupt Identification (IIR)                    | R   | Stores the four levels of prioritized interrupts and indicates the highest priority pending interrupt when read                    |  |

| Line Control (LCR)                                | R/W | Specifies the format of the asynchronous data communications exchange and set the DLAB                                             |  |

| Line Status (LSR)                                 | R   | Provides data transfer status information                                                                                          |  |

| Modem Control (MCR)                               | R/W | Provides control functions                                                                                                         |  |

| Modem Status (MSR)                                | R/W | Provides modem status information                                                                                                  |  |

| Receiver Buffer (RBR)                             | R   | Provides temporary storage for receive data                                                                                        |  |

| Scratch                                           | R/W | Provides a place where software can store data temporarily                                                                         |  |

| Speedsense Complete (SCR)                         | R   | Determines whether the Speedsense process is complete (1) or not complete (0)                                                      |  |

| Speedsense Value<br>Low/Med/High<br>(SVL/SVM/SVH) | R   | Matches the baudrate of the UART to that of the other modem device; reflects the low, middle, or high byte of the Speedsense value |  |

| Start Speedsense (SSR)                            | W   | Triggers the Speedsense function when any value to the register is written                                                         |  |

| Transmit Holding (THR)                            | W   | Provides temporary storage for transmit data                                                                                       |  |

#### 3.1.4 APB Timer Registers

The Timer register set consists of 13 registers, summarized in Table 3.4, which are accessed through the APB.

Table 3.4 APB Timer Register Summary

| Register Name                   | R/W | Description                                                                                                                               |

|---------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

| Timer 1/2                       | R/W | Returns the current value of the Timer on reads; updates the Timer at the next rising edge of the Timer 1/2 clock on writes               |

| Timer Control 1/2               | R/W | Controls specific Timer functions including freezing, up/down count, interval or periodic mode, and trigger point register selection      |

| Timer Prescaler 1/2             | R/W | Contains the value controlling the unit of time that each tick of<br>the Timer represents when combined with the input Timer 1/2<br>clock |

| Timer Trigger Control           | R/W | Selects between Timer 1 and Timer 2 to compare against the value held in each of the Timer Trigger Point registers                        |

| Timer Trigger Point 1/2/3/4/5/6 | R/W | Defines when an interrupt is generated                                                                                                    |

#### 3.1.5 Ethernet Controller Registers

All Ethernet Control registers are accessed over the APB.

The Ethernet Control register summary is shown in Table 3.5.

Table 3.5 Ethernet Controller Register Summary

| Register Name                                     | R/W | Description                                                                                                                  |  |  |

|---------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------|--|--|

| Carrier Loss Counter                              | R/W | Contains the number of times the carrier is lost in the middle of a Transmit frame since the last time the counter was read  |  |  |

| Collisions Counter: x (1–15) or More Back-to-Back | R/W | Contains the number of packets that collided $x$ (1–15) or more times before being transmitted                               |  |  |

| DMAC Configuration                                | R/W | Configures the AHB-Master DMA controller                                                                                     |  |  |

| DMAC Interrupt Enable                             | R/W | Enables the interrupts to the processor used to control the DMA                                                              |  |  |

| DMAC Interrupt Status                             | R/W | Provides status of the interrupts to the processor used to control the DMA                                                   |  |  |

| Ethernet Back-to-Back IPG                         | R/W | Programmable Transmit IPG for back-to-back transmissions                                                                     |  |  |

| Ethernet Interrupt Active                         | R   | Asserts the E110_INT signal                                                                                                  |  |  |

| Ethernet Interrupt Diagnostic                     | R/W | Generates an unconditional interrupt for test purposes; initializes the Transmit and Receive FIFOs for gate-level simulation |  |  |

Table 3.5 Ethernet Controller Register Summary (Cont.)

| Register Name                       | R/W | Description                                                                                                                                                                                                                                                                                                                      |  |

|-------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Ethernet Interrupt Enable           | R/W | Enables individual interrupt types selectively                                                                                                                                                                                                                                                                                   |  |

| Ethernet Interrupt Status           | R/W | Can be used to poll the interrupt flags; contains interrupt sta and is unaffected by interrupt enables                                                                                                                                                                                                                           |  |

| Ethernet IPG Part 1                 | R/W | Programmable transmit IPG Part 1 for non back-to-back transmissions                                                                                                                                                                                                                                                              |  |

| Ethernet IPG Part 2                 | R/W | Programmable transmit IPG Part 2 for non back-to-back transmissions                                                                                                                                                                                                                                                              |  |

| Ethernet MAC Address<br>(Bytes 1–4) | R/W | Address of the Ethernet device                                                                                                                                                                                                                                                                                                   |  |

| Ethernet MAC Address (Bytes 5–6)    | R/W | Address of the Ethernet device                                                                                                                                                                                                                                                                                                   |  |

| Ethernet Main Control               | R/W | Lets you reset the MAC, determine retransmission delay retries and wait times, and set full- or half-duplex mode                                                                                                                                                                                                                 |  |

| Ethernet MII Control Status         | R/W | Status information and control of MIIM functions to the MII PHY                                                                                                                                                                                                                                                                  |  |

| Ethernet MII Read                   | R   | Contains Status Register data read from the addressed MII PHY                                                                                                                                                                                                                                                                    |  |

| Ethernet MII Write                  | R/W | PHY and register address and write data for MII PHY register accesses                                                                                                                                                                                                                                                            |  |

| Ethernet Receive Control            | R/W | Controls Receive functions such as Virtual LAN protocol, Multicase block, Broadcase block, and Promiscuous Mode                                                                                                                                                                                                                  |  |

| Ethernet RNG Seed                   | R/W | Seed value to generate random number sequence used in collision backoff timing                                                                                                                                                                                                                                                   |  |

| Ethernet Transmit Control           | R/W | Controls transmit functions such as packet padding, preambl maximum packet size that can be transmitted, and CRC insertion                                                                                                                                                                                                       |  |

| Events Dropped Counter              | R/W | Contains the number of receive overruns since last read                                                                                                                                                                                                                                                                          |  |

| FCS/Alignment Errors Counter        | R/W | Contains the number of packets received since last read                                                                                                                                                                                                                                                                          |  |

| Flow Control                        | R/W | Enables transmit flow control when PAUSE frames are received; provides false carrier sense in half-duplex mode                                                                                                                                                                                                                   |  |

| Fragment Packets Counter            | R/W | Contains the number of packets received that are less than octets in length (excluding framing bits, but including FCS octets) and have either a bad FCS or a nonintegral number octets (Alignment Error)                                                                                                                        |  |

| Jabber Counter                      | R/W | Contains the number of packets received that are greater than 1518 octets for non-VLAN packets or if VLAN is disabled or greater than 1522 octets if VLAN is enabled and the packet a VLAN packet (excluding framing bits, but including FCS octets), and have either a bad FCS or a nonintegral number octets (Alignment Error) |  |

Table 3.5 Ethernet Controller Register Summary (Cont.)

| Register Name                    | R/W | Description                                                                                                                                                                                                                                                                           |  |

|----------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Late Collisions Counter          | R/W | Contains the number of late collisions that occurred since it was last read regardless of whether the Multiple Collisions (COL) interrupt is enabled                                                                                                                                  |  |

| Oversize Packets Counter         | R/W | Contains the number of packets received that are greater than 1518 octets for non-VLAN packets or if VLAN is disabled or greater than 1522 octets if VLAN is enabled and the packet is a VLAN packet (excluding framing bits, but including FCS octets) and are otherwise well-formed |  |

| Peripheral Reset                 | R   | Resets the peripheral                                                                                                                                                                                                                                                                 |  |

| Runt Packets Counter             | R/W | Contains the number of packets received that are less than 64 octets in length (excluding framing bits, but including FCS octets) and are otherwise well-formed                                                                                                                       |  |

| Receive Pointers                 | R   | Determines whether data is transferred to and from the Receive FIFO—for test purposes only                                                                                                                                                                                            |  |

| State                            | R   | Provides current state of match, receive and transmit state machines                                                                                                                                                                                                                  |  |

| Transmit Underruns Counter       | R/W | Contains the number of transmit underruns that occurred sin it was last read                                                                                                                                                                                                          |  |

| Transmit and Receive BMD Pointer | R/W | Contains the upper address of the first Transmit/Receive Buf Memory Descriptors (BMDs) in the lists                                                                                                                                                                                   |  |

| Transmit Pointers                | R   | Determines whether data is transferred to and from the Transmit FIFO—for test purposes only                                                                                                                                                                                           |  |

| Transmit Poll Timer              | R/W | Contains the number of clock cycles the transmit section must wait before polling a BMD with the valid bit cleared                                                                                                                                                                    |  |

| Transmit Threshold               | R/W | Controls how much data is required in the Transmit FIFO before the E-100 MAC starts transmitting                                                                                                                                                                                      |  |

## 3.1.6 Apl2c Registers

The Apl2c interface allows access for up to 64 addressable 16-bit registers aligned on 32-bit boundaries. The registers are used to control  $I^2C$  Master and Slave access to the  $I^2C$  bus. Reserved registers or fields are read-only and return all zeros when read.

The ApI2c registers are summarized in Table 3.6.

Table 3.6 Apl2c Register Summary

| Register Name                        | R/W | Description                                                                                                                                                             |  |  |

|--------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Global Control                       | R/W | Enables or disables the Master and Slave units independent enables and disables the IBML time-out timers globally                                                       |  |  |

| I <sup>2</sup> C Monitor             | R/W | Lets the host manually read and control the SCL and SDA I <sup>2</sup> C bus signals                                                                                    |  |  |

| IBML t <sub>LOW:MEXT</sub> Control   | R/W | Measures the time the SCL signal is extended LOW by the Master controller during data byte transmission or reception                                                    |  |  |

| IBML t <sub>LOW:SEXT</sub> Control   | R/W | Measures the time the SCL signal is extended LOW by the Slave controller during message transmission or reception                                                       |  |  |

| IBML t <sub>TIMEOUT</sub> Control    | R/W | Measures the time the SCL signal is detected LOW                                                                                                                        |  |  |

| Interrupt Enable                     | R/W | Enables/disables interrupt status reporting for the Master and Slave interrupt sources in the corresponding Interrupt Status Register bit and external interrupt signal |  |  |

| Interrupt Status                     | R/W | Reports the Master and Slave interrupt source status                                                                                                                    |  |  |

| Master Address Register 1            | R/W | Sent as the first byte in the address phase of an I <sup>2</sup> C transaction                                                                                          |  |  |

| Master Address Register 2            | R/W | Sent as the second byte in the address phase of an I <sup>2</sup> C transaction if ten-bit addressing is enabled                                                        |  |  |

| Master Command                       | R/W | Issues commands to the Master state machine                                                                                                                             |  |  |

| Master Data                          | R/W | Writes data into the Master Transmit FIFO, reads get data from the top of the Master Receive FIFO                                                                       |  |  |

| Master Interrupt Enable              | R/W | Enables/disables the individual Master interrupts; bits correspond to the Master Interrupt Status register bits                                                         |  |  |

| Master Interrupt Status              | R   | Records the status results of the last command issued                                                                                                                   |  |  |

| Master Receive Bytes<br>Transferred  | R   | Tracks the number of successfully received (acknowledged data bytes                                                                                                     |  |  |

| Master Receive FIFO Status           | R   | Indicates the number of data bytes currently in the Master Receive FIFO                                                                                                 |  |  |

| Master Receive Transfer Length       | R/W | Determines the number of bytes transferred during receive transfers                                                                                                     |  |  |

| Master Transmit Bytes<br>Transferred | R   | Tracks the number of successfully transmitted (acknowledged) data bytes                                                                                                 |  |  |

| Master Transmit FIFO Status          | R   | Indicates the number of data bytes currently in the Master Transmit FIFO                                                                                                |  |  |

| Master Transmit Transfer<br>Length   | R/W | Determines the number of data bytes sent during transmit transfers                                                                                                      |  |  |

| SCL High Period                      | R/W | Determines the high period for the SCL clock generated by I <sup>2</sup> 0 Master                                                                                       |  |  |

Table 3.6 Apl2c Register Summary (Cont.)

| Register Name                | R/W | Description                                                                                                                                                                                |  |

|------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SCL Low Period               | R/W | Determines the low period for the SCL clock generated by the I <sup>2</sup> C Master                                                                                                       |  |

| SDA Hold Time                | R/W | Controls the data hold time whenever the core controls SDA (Master or Slave)                                                                                                               |  |

| SDA Setup Time               | R/W | Controls the data setup time when the Master is driving SCL and SDA                                                                                                                        |  |

| Slave Address 1              | R/W | Contains the first I <sup>2</sup> C Slave address                                                                                                                                          |  |

| Slave Address 2              | R/W | Contains the second I <sup>2</sup> C Slave address                                                                                                                                         |  |

| Slave Address Decode Control | R/W | Enables/disables the two Slave address decoders and the General Call Address decode                                                                                                        |  |

| Slave Data                   | R/W | Provides access to Slave read or write data                                                                                                                                                |  |

| Slave Interrupt Enable       | R/W | Enables/disables the individual Slave interrupts; bits correspond to the Slave Interrupt Status register bits                                                                              |  |

| Slave Interrupt Status       | R   | Contains status information for Slave operations                                                                                                                                           |  |

| Slave Read Dummy Byte        | R/W | Provides a data byte for an I <sup>2</sup> C Master read transaction I <sup>2</sup> C Slave state machine has not received a data byte in Slave Data register before the SCL timer expires |  |

| Slave Receive FIFO Status    | R   | Provides access to the Receive Status FIFO which provides the status word for the data at the top of the Receive FIFO                                                                      |  |

| Slave Receive Control        | R/W | Controls the acknowledge cycle response during the data phase of a Slave write transfer                                                                                                    |  |

| Soft Reset                   | R/W | Lets the host independently clear the I <sup>2</sup> C interface                                                                                                                           |  |

| Spike Filter Length          | R/W | Controls the spike filter for SCL and SDA; filter stages determine the maximum size of the spike the filter suppress                                                                       |  |

| Timer Clock Divider Control  | R/W | Divides the APB clock frequency for use by all timers                                                                                                                                      |  |

| Wait Timer Control           | R/W | Controls the Master/Slave Wait Timer; times the different I <sup>2</sup> transactions and causes the appropriate state machine to tak action when time-out occurs                          |  |

#### 3.1.7 ApVic Registers

The ApVic contains registers, summarized in Table 3.7, that initialize and control interrupts within the system.

Table 3.7 ApVic Register Summary

| Register Name                              | R/W | Description                                                                                                                                |  |  |

|--------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Edge Select                                | R/W | Determines whether the interrupts are edge- or level-sensitive                                                                             |  |  |

| FIQ Current Priority Level (CPR)           | R/W | Sets the current priority level for the FIQ interrupts                                                                                     |  |  |

| FIQ Enable Clear                           | W   | Clears the corresponding bit in the FIQ Enable register when writing a 1; writing a 0 has no effect                                        |  |  |

| FIQ Enable Set                             | R/W | Sets up the mask for each interrupt that generates an interrupt into the nFIQ signal of the processor                                      |  |  |

| FIQ Index                                  | R/W | On reads this register contains the FIQ channel index location with the highest service priority; on writes it loads a hardware jump table |  |  |

| FIQ Interrupt Service Routine (ISR) Vector | R/W | Contains the starting address vector of the ISR for the FIQ interrupt with the highest service priority                                    |  |  |

| FIQ Last Priority Level (LPR)              | R   | Returns the last priority level for the FIQ interrupts                                                                                     |  |  |

| FIQ Raw Status/Clear                       | R/W | Contains the premasked interrupts on reads; on writes, it clears active interrupts                                                         |  |  |

| FIQ Status                                 | R   | Contains postmasked interrupts ORed together to form the FIQ interrupt                                                                     |  |  |

| IRQ Current Priority Level (CPR)           | R/W | Sets the current priority level for the IRQ interrupts                                                                                     |  |  |

| IRQ Enable Clear                           | W   | Clears the corresponding bit in the IRQ Enable register wh writing a 1; writing a 0 has no effect                                          |  |  |

| IRQ Enable Set                             | R/W | Sets up the mask for each interrupt that can generate an interrupt to the processor nIRQ output                                            |  |  |

| IRQ Index                                  | R/W | On Reads this register contains the IRQ channel index location with the highest service priority; on Writes it loads a hardware jump table |  |  |

| IRQ Interrupt Service Routine (ISR) Vector | R/W | Contains the starting address vector of the ISR for the IRC interrupt with the highest service priority                                    |  |  |

| IRQ Last Priority Level (LPR)              | R   | Returns the last priority level for the IRQ interrupts                                                                                     |  |  |

| IRQ Raw Status/Clear                       | R/W | Contains the premasked interrupts when read; on writes, the Clear register clears active interrupts                                        |  |  |

| IRQ Status                                 | R   | Contains postmasked interrupts ORed together to form the IRQ interrupt                                                                     |  |  |

| IRQ/FIQ Soft Interrupt                     | R/W | Sets a software interrupt                                                                                                                  |  |  |

Table 3.7 ApVic Register Summary (Cont.)

| Register Name            | R/W | Description                                                                                            |

|--------------------------|-----|--------------------------------------------------------------------------------------------------------|

| Polarity Select          | R/W | Determines whether a HIGH or LOW state on each INTERRUPTS[31:0] input causes an interrupt              |

| Priority Table Channel x | R/W | Sets channel priorities; there are 32 Priority Table Channel registers, one for each interrupt channel |

| Resync Select            | R/W | Determines whether or not the external interrupts are resynced internally                              |

#### 3.1.8 Remap Register

The remap peripheral located on the APB bus has only one register located at offset 0x0 from the remap base address.

Table 3.8 Chip Select Control Register Summary

| Register Name  | R/W | Description                                                                                                                                                                                            |

|----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Remap Register |     | Lets you change the address map after reset when writing to<br>the Remap bit (Remap register bit 0); read this register to<br>determine the address map currently used by the system<br>decoding logic |

### 3.2 System Memory Map

This section summarizes the system boot settings and memory maps.

#### 3.2.1 System Boot Settings

The boot method is selected by using the strap pins BRBOOTSEL, VINITHI, and INITRAM. These three pins determine which device and which address location the ARM926EJ-S processor uses. Possible boot devices are the External SRAM, an external slave connected to the AHB Slave Expansion Port using the Segmentation Bridge, or the Instruction TCM, if the Processor System for ARM926EJ-S supports the use of TCMs. Check the ARM926EJ-S processor datasheet.

The system memory maps and decoding support the boot methods shown in Table 3.9 and Table 3.10.

Table 3.9 System Boot Setting: BRBOOTSEL=0

|                         | BRBOOTSEL = 0              |                            |                            |                            |  |  |  |  |  |

|-------------------------|----------------------------|----------------------------|----------------------------|----------------------------|--|--|--|--|--|

| Address                 | VINITHI = 0<br>INITRAM = 0 | VINITHI = 1<br>INITRAM = 0 | VINITHI = 0<br>INITRAM = 1 | VINITHI = 1<br>INITRAM = 1 |  |  |  |  |  |

| 0x0000.0000-0x0FFF.FFFF | External SRAM              | _                          | Instruction TCM            | _                          |  |  |  |  |  |

| 0x1000.0000-0xEFFF.FFFF | _                          | _                          | _                          | _                          |  |  |  |  |  |

| 0xF000.0000-0xFFFF.FFFF | _                          | External SRAM              | _                          | External SRAM              |  |  |  |  |  |

Table 3.10 System Boot Setting: BRBOOTSEL=1

|                         | BRBOOTSEL = 1              |                            |                            |                            |  |  |

|-------------------------|----------------------------|----------------------------|----------------------------|----------------------------|--|--|

| Address                 | VINITHI = 0<br>INITRAM = 0 | VINITHI = 1<br>INITRAM = 0 | VINITHI = 0<br>INITRAM = 1 | VINITHI = 1<br>INITRAM = 1 |  |  |

| 0x0000.0000-0x0FF.FFFF  | Segmentation<br>Bridge     | _                          | Instruction TCM            | _                          |  |  |

| 0x1000.0000-0xEFFF.FFFF | _                          | _                          | _                          | _                          |  |  |

| 0xF000.0000–0xFFF.FFFF  | _                          | Segmentation<br>Bridge     | _                          | Segmentation<br>Bridge     |  |  |

#### 3.2.2 Memory Map and Addressing

Table 3.11, Table 3.12, Table 3.13, and Table 3.14 show the I-AHB and D-AHB memory maps. Table 3.15 provides an address map for the APB peripherals. Together, these maps specify the memory addresses for every peripheral in the system.

Table 3.11 Address Map for Instruction AHB Bus—TCMs Disabled<sup>1</sup>

|                                                              |                                                                 | BRBOOTSEL State                          |                             |                                       |                             |               |  |  |

|--------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------|-----------------------------|---------------------------------------|-----------------------------|---------------|--|--|

| Device on Instruction<br>AHB Bus                             |                                                                 | BRBOOTSEL = 0<br>(SRAM, Flash, ROM Port) |                             | BRBOOTSEL = 1<br>(AHB Slave Exp Port) |                             | - Memory      |  |  |

|                                                              |                                                                 | After Reset                              | After Remap                 | After Reset                           | After Remap                 | Space         |  |  |

| ARM926EJ-S TCMs &<br>External Memory                         | Instruction TCM (1 Mbyte max)                                   |                                          |                             |                                       |                             | 256<br>Mbytes |  |  |

|                                                              | Data TCM<br>(1 Mbyte max)                                       |                                          |                             |                                       |                             |               |  |  |

|                                                              | External SRAM                                                   | 0x0000.0000-<br>0x0FFF.FFFF              |                             |                                       |                             |               |  |  |

|                                                              | Segmentation<br>Bridge (AHB<br>Slave Expansion<br>Port)         |                                          |                             | 0x0000.0000-<br>0x0FFF.FFFF           |                             |               |  |  |

|                                                              | Multiport Memory<br>Controller Port<br>with select pin<br>IHSEL |                                          | 0x0000.0000-<br>0x0FFF.FFFF |                                       | 0x0000.0000-<br>0x0FFF.FFFF |               |  |  |

| Multiport Memory<br>Controller Port with<br>select pin IHSEL |                                                                 | 0x1000.0000–0x7FFF.FFFF                  |                             |                                       |                             |               |  |  |

| Segmentation Bridge<br>(AHB Slave Expansion<br>Port)         |                                                                 |                                          | 1.5<br>Gbytes               |                                       |                             |               |  |  |