# SALEM<sup>®</sup> Three-Phase Electronic Energy Meter

# ADSST-EM-3035

#### FEATURES

IEC 687, Class 0.5 and Class 0.2 Accuracy **ANSI C12.1** IEC 1268, Requirements for Reactive Power Configurable as Import/Export or Import Only Simultaneous Measurement of: Active Power and Energy-Import and Export **Reactive Power and Energy Apparent Power Power Factor for Individual Phases and Total Frequency RMS Voltage for All Phases RMS Current for All Phases** Harmonic Analysis for Voltage and Current All Odd Harmonics up to 21st Order Interface with a General Purpose Microcontroller User-Friendly Calibration of Gain Offset and Phase and Nonlinearity Compensation on CTs (Patent Pending) **Two Programmable Output E-Pulses** Programmable E-Pulse Constant from 1,000 Pulses/kWh to 20,000 Pulses/kWh 15 kHz Sampling Frequency **Tamper-Proof Metering** Single 5 V Supply

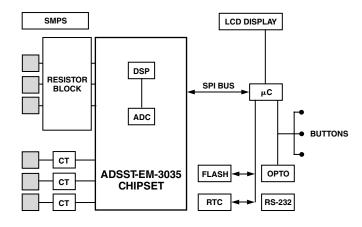

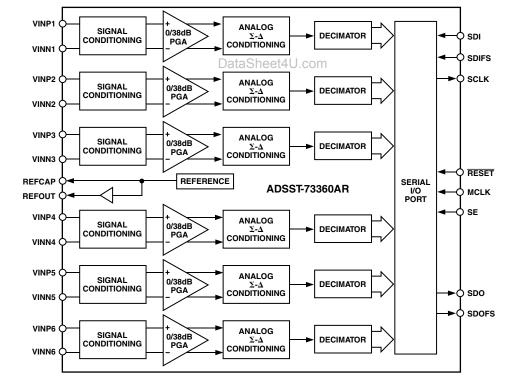

#### FUNCTIONAL BLOCK DIAGRAM

DataShe

DataSheet4U.com

#### GENERAL DESCRIPTION

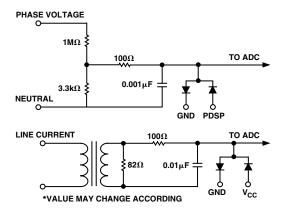

The ADSST-EM-3035 Chipset consists of a fast and accurate 6 channel, 16-bit sigma-delta analog-to-digital converter ADSST-73360AR (ADC), an efficient digital signal processor ADSST-2185KST-133 (DSP), and Metering Software. The ADC and DSP are interfaced together to simultaneously acquire voltage and current samples on all the three phases and perform mathematically intensive computations to accurately calculate the Powers, Energies, Instantaneous Quantities, and Harmonics. The chipset could be interfaced to any general-purpose microprocessor to develop state of the art polyphase or Tri-vector energy metering solution in accordance with IEC 1036, IEC 687, or ANSI C12.1.

All calibrations are done in digital domain and no trimming potentiometers are required.

SALEM is a registered trademark of Analog Devices, Inc.

#### REV.0

Information furnished by Analog Devices is believed to be accurate and DataSheet4 reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

WWW.DataSheet4U.com One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 2002

ADSST\_2185KST\_133 (DSP) SPECIFIC ATION

|   | ADSST-2185KST-133 (DSP) SPECIFICATION                           | GENERAL DES                          |

|---|-----------------------------------------------------------------|--------------------------------------|

|   | FEATURES                                                        | The ADSST-218                        |

|   | 30 ns Instruction Cycle 33 MIPS Sustained Performance           | optimized for dig                    |

|   | Single-Cycle Instruction Execution                              | speed numeric pr                     |

|   | Single-Cycle Context Switch                                     | The ADSST-218                        |

|   | Three-Bus Architecture Allows Dual Operand Fetches              | base architecture                    |

|   | in Every Instruction Cycle                                      | generators, and a                    |

|   | Multifunction Instructions                                      | 16-bit internal D                    |

|   | Power-Down Mode Featuring Low CMOS Standby Power                | timer, Flag I/O, e                   |

|   | Dissipation with 100 Cycle Recovery from Power-Down             | program and data                     |

|   | Condition                                                       |                                      |

|   | Low Power Dissipation in Idle Mode                              | The ADSST-218                        |

|   | ADSP-2100 Family Code Compatible, with Instruction              | memory configur                      |

|   | Set Extensions                                                  | 8 Kwords (16-bit                     |

|   | 40 kBytes of On-Chip RAM, Configured as                         | provided to meet                     |

|   | 8 KWords On-Chip Program Memory RAM and                         | equipment. The A                     |

|   | 8 KWords On-Chip Data Memory RAM                                | TQFP package.                        |

|   | Dual Purpose Program Memory for Both Instruction                | In addition, the A                   |

|   | and Data Storage                                                | that include bit n                   |

|   | Independent ALU, Multiplier/Accumulator, and Barrel             | test new ALU con                     |

|   | Shifter Computational Units                                     | biased rounding,                     |

|   | Two Independent Data Address Generators                         | fers, and global in                  |

|   | Powerful Program Sequencer Provides Zero Overhead               | Fabricated in a h                    |

|   | Looping Conditional Instruction Execution                       | process, the ADS                     |

|   | Programmable 16-Bit Interval Timer with Prescaler               | instruction cycle                    |

|   | 100-Lead TQFP                                                   | processor cycle.                     |

|   | 16-Bit Internal DMA Port for High Speed Access to On-           |                                      |

| n | Chip Memory (Mode Selectable)                                   | The ADSST-218                        |

|   | A Montes Dute Memory Interface for Starsus of Date              | prehensive instru                    |

|   | Tables and Program Overlays DataSh                              | multiple operation                   |

|   | 8-Bit DMA to Byte Memory for Transparent Program and            | ADSST-2185KS                         |

|   | Data Memory Transfers (Mode Selectable)                         | • Generate the n                     |

|   | I/O Memory Interface with 2048 Locations Supports               | • Fetch the next                     |

|   | Parallel Peripherals (Mode Selectable)                          |                                      |

|   | Programmable Memory Strobe and Separate I/O                     | • Perform one on                     |

|   | Memory Space Permits Glueless System Design                     | • Update one or                      |

|   | (Mode Selectable)                                               | • Perform a com                      |

|   | Programmable Wait State Generation                              |                                      |

|   | Two Double-Buffered Serial Ports with Companding                | <ul> <li>This takes place</li> </ul> |

|   | Hardware and Automatic Data Buffering                           | Receive and                          |

|   | Automatic Booting of On-Chip Program Memory from                | Receive and/                         |

|   | Byte-Wide External Memory, e.g., EPROM, or through              | Receive and/                         |

|   | Internal DMA Port                                               |                                      |

|   | Six External Interrupts                                         | Decrement t                          |

|   | 13 Programmable Flag Pins Provide Flexible System Signaling     |                                      |

|   | UART Emulation through Software SPORT Reconfiguration           |                                      |

|   | ICE-Port Emulator Interface Supports Debugging in Final Systems | DATA ADDRESS                         |

|   |                                                                 | GENERATORS PROG                      |

|   |                                                                 | DAG1 DAG2                            |

|   |                                                                 |                                      |

|   |                                                                 |                                      |

|   |                                                                 |                                      |

|   |                                                                 |                                      |

|   |                                                                 | <u>رم</u>                            |

|   |                                                                 |                                      |

|   |                                                                 | ARITHMETIC UNITS                     |

|   |                                                                 |                                      |

#### GENERAL DESCRIPTION

85KST-133 is a single-chip microcomputer gital signal processing (DSP) and other high processing applications.

85KST-133 combines the ADSP-2100 family e (three computational units, data address a program sequencer) with two serial ports, a DMA port, a byte DMA port, a programmable extensive interrupt capabilities, and on-chip a memory.

85KST-133 integrates 40 kBytes of on-chip red as 8 Kwords (24-bit) of program RAM and it) of data RAM. Power-down circuitry is also the low power needs of battery operated portable ADSST-2185KST-133 is available in a 100-lead

ADSST-2185KST-133 supports instructions manipulations, bit set, bit clear, bit toggle, bit nstants, new multiplication instruction (x squared), result free ALU operations, I/O memory transinterrupt masking for increased flexibility.

high speed, double metal, low power, CMOS SST-2185KST-133 operates with a 25 ns time. Every instruction can execute in a single

85KST-133's flexible architecture and comruction set allow the processor to perform ions in parallel. In one processor cycle, the ST-133 can:

- next program address

- t instruction

- r two data moves

- r two data address pointers

- nputational operation

- ce while the processor continues to:

- transmit data through the two serial ports

- l/or transmit data through the internal DMA port

- l/or transmit data through the byte DMA port

- timer

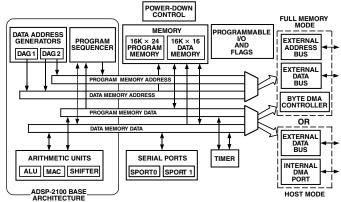

www.DataSheet4U.com Figure 1. Functional Block Diagram

#### **ARCHITECTURE OVERVIEW**

The ADSST-2185KST-133 instruction set provides flexible data moves and multifunction (one or two data moves with a computation) instructions. Every instruction can be executed in a single processor cycle. The ADSST-2185KST-133 assembly language uses an algebraic syntax for ease of coding and readability. A comprehensive set of development tools supports program development.

Figure 1 is an overall block diagram of the ADSST-2185KST-133. The processor contains three independent computational units: the ALU, the multiplier/accumulator (MAC), and the shifter. The computational units process 16-bit data directly and have provisions to support multiprecision computations. The ALU performs a standard set of arithmetic and logic operations; division primitives are also supported. The MAC performs single-cycle multiply, multiply/add and multiply/subtract operations with 40 bits of accumulation. The shifter performs logical and arithmetic shifts, normalization, denormalization and derive exponent operations.

The shifter can be used to efficiently implement numeric format control including multiword and block floating-point representations.

The internal result (R) bus connects the computational units so the output of any unit may be the input of any unit on the next cycle.

A powerful program sequencer and two dedicated data address generators ensure efficient delivery of operands to these computational units. The sequencer supports conditional jumps, subroutine calls, and returns in a single cycle. With internal loop counters and loop stacks, the ADSST-2185KST-133 executes looped code with zero overhead. No explicit jump instructions are required to maintain loops.

Two data address generators (DAGs) provide addresses for simultaneous dual operand fetches from data memory and program memory. Each DAG maintains and updates four address pointers. Whenever the pointer is used to access data (indirect addressing), it is postmodified by the value of one of four possible modify registers. A length value may be associated with each pointer to implement automatic modulo addressing for circular buffers.

Efficient data transfer is achieved with the use of five internal buses:

- Program Memory Address (PMA) Bus

- Program Memory Data (PMD) Bus

- Data Memory Address (DMA) Bus

- Data Memory Data (DMD) Bus

- Result (R) Bus

The two address buses (PMA and DMA) share a single external address bus, allowing memory to be expanded off-chip, and the two data buses (PMD and DMD) share a single external data bus. Byte memory space and I/O memory space also share the external buses.

Program memory can store both instructions and data, permitting the ADSST-2185KST-133 to fetch two operands in a single cycle, one from program memory and one from data memory. The ADSST-2185KST-133 can fetch an operand from program memory and the next instruction in the same cycle.

When configured in host mode, the ADSST-2185KST-133 has a 16-bit Internal DMA port (IDMA port) for connection to external systems. The IDMA port is made up of 16 data/address pins and five control pins. The IDMA port provides transparent, direct access to the DSP's on-chip program and data RAM.

An interface to low cost byte-wide memory is provided by the Byte DMA port (BDMA port). The BDMA port is bidirectional and can directly address up to four megabytes of external RAM or ROM for off-chip storage of program overlays or data tables.

The byte memory and I/O memory space interface supports slow memories and I/O memory-mapped peripherals with programmable wait state generation. External devices can gain control of external buses with bus request/grant signals ( $\overline{BR}$ ,  $\overline{BGH}$ , and  $\overline{BG}$ ). One execution mode (Go Mode) allows the ADSST-2185KST-133 to continue running from on-chip memory. Normal execution mode requires the processor to halt while buses are granted.

The ADSST-2185KST-133 can respond to 11 interrupts. There are up to six external interrupts (one edge-sensitive, two level-sensitive, and three configurable) and seven internal interrupts generated by the timer, the serial ports (SPORTs), the Byte DMA port, and the power-down circuitry. There is also a master  $\overline{\text{RESET}}$  signal. The two serial ports provide a complete synchronous serial interface with optional companding in hardware and a wide variety of framed or frameless data transmit and receive modes of operation.

Each port can generate an internal programmable serial clock or accept an external serial clock.

The ADSST-2185KST-133 provides up to 13 general purpose flag pins. The data input and output pins on SPORT1 can be alternatively configured as an input flag and an output flag. In addition, eight flags are programmable as inputs or outputs, and DataShee three flags are always outputs.

A programmable interval timer generates periodic interrupts. A 16-bit count register (TCOUNT) decrements every n processor cycle, where n is a scaling value stored in an 8-bit register (TSCALE). When the value of the count register reaches zero, an interrupt is generated and the count register is reloaded from a 16-bit period register (TPERIOD).

#### Serial Ports

The ADSST-2185KST-133 incorporates two complete synchronous serial ports (SPORT0 and SPORT1) for serial communications and multiprocessor communication.

Here is a brief list of the capabilities of the ADSST-2185KST-133 SPORTs. For additional information on Serial Ports, refer to the ADSP-2100 Family User's Manual, Third Edition.

- SPORTs are bidirectional and have a separate, double-buffered transmit and receive section.

- SPORTs can use an external serial clock or generate their own serial clock internally.

- SPORTs have independent framing for the receive and transmit sections. Sections run in a frameless mode or with frame synchronization signals internally or externally generated. Frame sync signals are active high or inverted, with either of two pulsewidths and timings.

- SPORTs support serial data word lengths from 3 to 16 bits and provide optional A-law and M-law companding according to CCITT recommendation G.711.

- SPORT receive and transmit sections can generate unique interrupts on completing a data-word transfer.

- SPORTs can receive and transmit an entire circular buffer of. data with only one overhead cycle per data-word. An interrupt is generated after a data buffer transfer.

**REV.0**

- SPORT0 has a multichannel interface to selectively receive and transmit a 24- or 32-word, time-division multiplexed, serial bitstream.

- SPORT1 can be configured to have two external interrupts (IRQ0 and IRQ1) and the Flag In and Flag Out signals. The internally generated serial clock may still be used in this configuration.

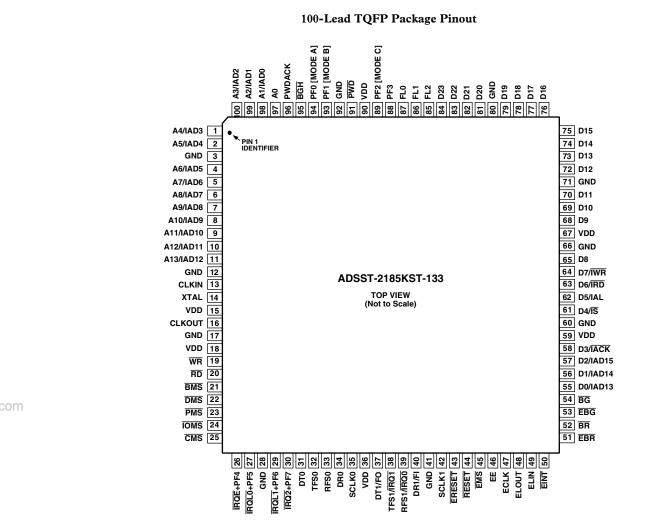

#### **Pin Descriptions**

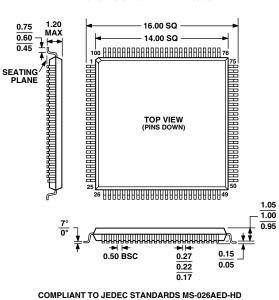

The ADSST-2185KST-133 is available in a 100-lead TQFP package. To maintain maximum functionality and reduce package size and pin count, some serial ports, programmable flags, interrupt and external bus pins have dual, multiplexed functionality. The external bus pins are configured during RESET only, while serial port pins are software configurable during program execution. Flag and interrupt functionality is retained concurrently on multiplexed pins. In cases where pin functionality is reconfigurable, the default state is shown in plain text; alternate functionality is shown in italics.

| Pin<br>Name(s) | Number<br>of Pins |     | Function                        | Pin<br>Name(s)                                                       | Number<br>of Pins |              | Function                                   |  |

|----------------|-------------------|-----|---------------------------------|----------------------------------------------------------------------|-------------------|--------------|--------------------------------------------|--|

| RESET          | 1                 | I   | Processor Reset Input           | PF0 (Mode A)                                                         | 1                 | Ι            | Mode Select Input-Checked                  |  |

| BR             | 1                 | I   | Bus Request Input               |                                                                      |                   |              | only During RESET                          |  |

| BG             | 1                 | 0   | Bus Grant Output                | CLKIN,                                                               | 2                 | Ι            | Clock or Quartz Crystal Input              |  |

| BGH            | 1                 | 0   | Bus Grant Hung Output           | XTAL                                                                 |                   |              |                                            |  |

| DMS            | 1                 | 0   | Data Memory Select Output       | CLKOUT                                                               | 1                 | 0            | Processor Clock Output                     |  |

| PMS            | 1                 | 0   | Program Memory Select Output    | SPORT0                                                               | 5                 | I/O          | Serial Port I/O Pins                       |  |

| IOMS           | 1                 | 0   | Memory Select Output            | SPORT1                                                               | 5                 | I/O          | Serial Port I/O Pins                       |  |

| BMS            | 1                 | 0   | Byte Memory Select Output       | IRQ1:0                                                               |                   |              | Edge- or Level-Sensitive                   |  |

| CMS            | 1                 | 0   | Combined Memory                 | -                                                                    |                   |              | Interrupts                                 |  |

|                |                   |     | Select Output                   | F1, F0                                                               |                   |              | Flag In, Flag Out <sup>2</sup>             |  |

| RD             | 1                 | 0   | Memory Read Enable Output       | PWD                                                                  | 1                 | Ι            | Power-Down Control Input                   |  |

| WR             | 1                 | 0   | Memory Read Enable Output       | PWDACK                                                               | 1                 | 0            | Power-Down Control Output                  |  |

| IRQ2+PF7       | 1                 | I   |                                 | FL0, FL1,                                                            | 3                 | 0            | Output Flags                               |  |

| -              |                   |     | Interrupt Request <sup>1</sup>  | FL2                                                                  |                   |              |                                            |  |

| IRQL0+PF5      | 1                 | I   | Level-Sensitive                 | VDD                                                                  | 16                | Ι            | VDD and GND                                |  |

| -              |                   |     | Interrupt Requests <sup>1</sup> | AND                                                                  |                   |              |                                            |  |

| IRQL1+PF6      | 1                 | I   | Level-Sensitive                 | GND                                                                  |                   |              |                                            |  |

| -              |                   |     | Interrupt Requests <sup>1</sup> | EX-Port                                                              | 9                 | I/O          | For Emulation Use                          |  |

| IRQE+PF4       | 1                 | I   | Edge-Sensitive                  | NOTES                                                                |                   |              |                                            |  |

| -              |                   |     | Interrupt Requests <sup>1</sup> |                                                                      | ins retain bot    | h functions  | concurrently. If IMASK is set to enabl     |  |

| PF3            | 1                 | I/O | Programmable I/O Pin            | the corresponding interrupts, the DSP will vector to the appropriate |                   |              |                                            |  |

| PF2 (Mode C)   | 1                 | I   | Programmable I/O Pin Mode       |                                                                      |                   | is asserted, | either by external devices or set as a     |  |

|                |                   |     | Select Input-Checked only       | programmable f                                                       |                   |              | DSD Strategy Constrait Desiration Software |  |

|                |                   |     | During RESET                    | configurable.                                                        | ration determ     | med by the   | DSP System Control Register. Softwar       |  |

| PF1 (Mode B)   | 1                 | Ι   | Mode Select Input-Checked       | comgatuole.                                                          |                   |              |                                            |  |

|                |                   |     | only During RESET               |                                                                      |                   |              |                                            |  |

Table I. Common-Mode Pins

et4U.com

DataSheet4U.com

REV. 0 DataSheet4U.com

#### System Interface

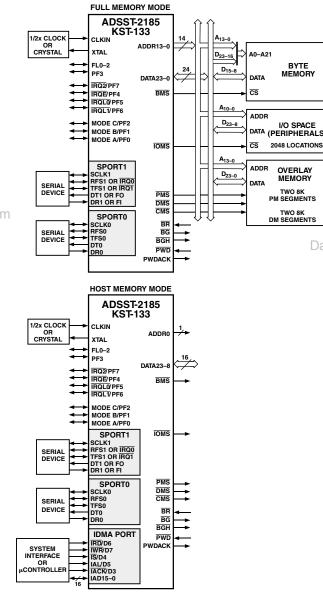

Figure 2 shows typical basic system configurations with the ADSST-2185KST-133, two serial devices, a byte-wide EPROM and optional external program and data overlay memories (mode selectable). Programmable wait state generation allows the processor to connect easily to slow peripheral devices. The ADSST-2185KST-133 also provides four external interrupts and two serial ports, or six external interrupts and one serial port. Host Memory Mode allows access to the full external data bus, but limits addressing to a single address bit (A0). Additional system peripherals can be added in this mode through the use of external hardware to generate and latch address signals.

Figure 2. Basic System Interface

**Recommended Operating Conditions**

| Demonsterne                               | -   | rade<br>Max |     | brade<br>Max | TT.  |

|-------------------------------------------|-----|-------------|-----|--------------|------|

| Parameters                                | Min | Max         | Min | max          | Unit |

| V <sub>DD</sub> Supply Voltage            | 4.5 | 5.5         | 4.5 | 5.5          | V    |

| $V_{DD}$ Supply Voltage $T_{AMB}$ Ambient | 0   | +70         | -40 | +85          | °C   |

| Operating Temperature                     |     |             |     |              |      |

#### **Clock Signals**

Either a crystal or a TTL-compatible clock signal can clock the ADSST-2185KST-133.

The CLKIN input cannot be halted, changed during operation, or operated below the specified frequency during normal operation. The only exception is while the processor is in the power-down state. For additional information, refer to Chapter 9, ADSP-2100 Family User's Manual, Third Edition, for detailed information on this power-down feature.

If an external clock is used, it should be a TTL-compatible signal running at half the instruction rate. The signal is connected to the processor's CLKIN input. When an external clock is used, the XTAL input must be left unconnected.

The ADSST-2185KST-133 uses an input clock with a frequency equal to half the instruction rate; a 20.00 MHz input clock yields a 25 ns processor cycle (which is equivalent to 40 MHz). Normally, instructions are executed in a single processor cycle. All device timing is relative to the internal instruction clock rate, which is indicated by the CLKOUT signal when enabled.

Because the ADSST-2185KST-133 includes an on-chip oscillator circuit, an external crystal may be used. The crystal should be connected across the CLKIN and XTAL pins, with two capacitors connected as shown in Figure 3. Capacitor values are dependent on crystal type and should be specified by the crystal manufacturer. A parallel-resonant, fundamental frequency, microprocessorgrade crystal should be used.

#### Figure 3. External Crystal Connections

A clock output (CLKOUT) signal is generated by the processor at the processor's cycle rate. This can be enabled and disabled by the CLKODIS bit in the SPORT0 Autobuffer Control Register.

#### Reset

BYTE MEMORY

The **RESET** signal initiates a master reset of the ADSST-2185KST-133. The RESET signal must be asserted during the power-up sequence to assure proper initialization. RESET during initial power-up must be held long enough to allow the internal clock to stabilize. If RESET is activated any time after power-up, the clock continues to run and does not require stabilization time.

The power-up sequence is defined as the total time required for the crystal oscillator circuit to stabilize after a valid VDD is applied to the processor, and for the internal phase-locked loop (PLL) to lock onto the specific crystal frequency. A minimum of 2000 CLKIN cycles ensures that the PLL has locked, but does not include the crystal oscillator start-up time. During this powerup sequence, the  $\overline{\text{RESET}}$  signal should be held low. On any subsequent resets, the  $\overline{\text{RESET}}$  signal must meet the minimum pulsewidth specification, t<sub>RSP</sub>.

The **RESET** input contains some hysteresis; however, if you use an RC circuit to generate your **RESET** signal, the use of an external Schmidt trigger is recommended. The master reset sets all internal stack pointers to the empty stack condition, masks all interrupts and clears the MSTAT register. When  $\overline{\text{RESET}}$  is released, if there is no pending bus request and the chip is configured for booting, the boot-loading sequence is performed The first instruction is fetched from on-chip program memory location 0x0000 once boot loading completes.

### ELECTRICAL CHARACTERISTICS

|                  |                                              |                                        | F                     | K/B Grade | :   |      |  |

|------------------|----------------------------------------------|----------------------------------------|-----------------------|-----------|-----|------|--|

| Parameters       |                                              | Test Conditions                        | Min                   | Тур       | Max | Unit |  |

| VIH              | High-Level Input Voltage <sup>1, 2</sup>     | (a) $V_{DD} = max$                     | 2.0                   |           |     | V    |  |

| V <sub>IH</sub>  | High-Level CLKIN Voltage                     | $(a) V_{DD} = max$                     | 2.2                   |           |     | V    |  |

| V <sub>IL</sub>  | Low-Level Input Voltage <sup>1, 3</sup>      | $(a) V_{DD} = min$                     |                       |           | 0.8 | V    |  |

| V <sub>OH</sub>  | High-Level Output Voltage <sup>1, 4, 5</sup> | $(a) V_{DD} = min$                     |                       |           |     |      |  |

|                  |                                              | $I_{OH} = -0.5 \text{ max}$            | 2.4                   |           |     | V    |  |

|                  |                                              | $(a) V_{DD} = min$                     |                       |           |     |      |  |

|                  |                                              | $I_{OH} = -100 \ \mu A^6$              | V <sub>DD</sub> - 0.3 |           |     | V    |  |

| V <sub>OL</sub>  | Low-Level Output Voltage <sup>1, 4, 5</sup>  | (a) V <sub>DD</sub> = min              |                       |           | 0.4 | V    |  |

|                  |                                              | $I_{OL} = 2 \text{ mA}$                |                       |           |     |      |  |

| I <sub>IH</sub>  | High-Level Input Current <sup>3</sup>        | (a) V <sub>DD</sub> = max              |                       |           |     |      |  |

|                  |                                              | $\overrightarrow{V}_{IN} = V_{DD} max$ |                       |           | 10  | μA   |  |

| I <sub>IL</sub>  | Low-Level Input Current <sup>3</sup>         | $@V_{DD} = max$                        |                       |           |     |      |  |

|                  |                                              | $V_{IN} = 0 V$                         |                       |           | 10  | μA   |  |

| I <sub>OZH</sub> | Three-State Leakage Current <sup>7</sup>     | $@V_{DD} = max$                        |                       |           |     |      |  |

|                  |                                              | $V_{IN} = V_{DD} max$                  |                       |           | 10  | μA   |  |

| I <sub>OZL</sub> | Three-State Leakage Current <sup>7</sup>     | $@V_{DD} = max$                        |                       |           |     |      |  |

|                  |                                              | $V_{IN} = 0 V^8$                       |                       |           | 10  | μA   |  |

| I <sub>DD</sub>  | Supply Current (Idle) <sup>9</sup>           | (a) $V_{DD} = 5.0$                     |                       | 12.4      |     | mA   |  |

| I <sub>DD</sub>  | Supply Current                               | (a) $V_{DDINT} = 5.0$                  |                       |           |     |      |  |

|                  | (Dynamic) <sup>10, 11</sup>                  | $T_{AMB} = 25^{\circ}C$                |                       |           |     |      |  |

|                  |                                              | $t_{\rm CK} = 30 \ {\rm ns}^{11}$      |                       | 55        |     | mA   |  |

|                  |                                              | $t_{CK} = 25 \text{ ns}^{11}$          |                       | [65]      |     | mA   |  |

| CI               | Input Pin                                    | (a) $V_{IN} = 2.5 V$ ,                 |                       |           |     |      |  |

|                  | Capacitance <sup>3, 6, 12</sup>              | $f_{IN}$ = 1.0 MHz,                    |                       |           |     |      |  |

|                  |                                              | $T_{AMB} = 25^{\circ}C$                |                       |           | 8   | pF   |  |

| Co               | Output Pin                                   | $V_{IN} = 2.5 V,$                      |                       |           |     |      |  |

|                  | Capacitance <sup>6, 7, 12, 13</sup>          | $f_{IN} = 1.0 MHz$ ,                   |                       |           |     |      |  |

|                  |                                              | $T_{AMB} = 25^{\circ}C$                |                       |           | 8   | pF   |  |

NOTES

<sup>1</sup>Bidirectional pins: D0–D23, RFS0, RFS1, SCLK0, SCLK1, TFS0, TFS1, A1–A13, PF0–PF7.

<sup>2</sup>Input only pins: <u>DC-D2</u>, KPSU, KPSU, KPSU, SCLKU, 1150, 1151, AT-ATS, 110-117. <sup>2</sup>Input only pins: <u>RESET</u>, <u>BR</u>, DR0, DR1, <u>PWD</u>. <sup>4</sup>Output pins: <u>BG</u>, <u>PMS</u>, <u>DMS</u>, <u>BMS</u>, <u>TOMS</u>, <u>CMS</u>, <u>RD</u>, <u>WR</u>, PWDACK, A0, DT0, DT1, CLKOUT, FL2-0, <u>BGH</u>. <sup>5</sup>Although specified for TTL outputs, all ADSST-2185KST-133 outputs are CMOS-compatible and will drive to V<sub>DD</sub> and GND, assuming no dc loads.

<sup>6</sup>Guaranteed but not tested.

<sup>7</sup>Three-statable pins: A0–A13, D0, D23, PMS, DMS, BMS, IOMS, CMS, RD, WR, DT0, DT1, SCLK0, SCLK1, TFS0, TFS1, RFS0, RFS1, PF0, PF7. <sup>8</sup>0 V on BR, CLKIN inactive.

$^9$ Idle refers to ADSST-2185KST-133 state of operation during execution of IDLE instruction. Deasserted pins are driven to either V  $_{

m DD}$  or GND.

<sup>10</sup>I<sub>DD</sub> measurement taken with all instructions executing from internal memory. 50% of the instructions are multifunction (types 1, 4, 5, 12, 13, 14), 30% are type 2 and type 6, and 20% are idle instructions.

$^{11}V_{IN} = 0$  V and 3 V. For typical figures for supply currents, refer to Power Dissipation section.

<sup>12</sup>Applies to TQFP package type

<sup>13</sup>Output pin capacitance is the capacitive load for any three-stated output pin.

Specifications subject to change without notice.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Supply Voltage                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------|

| Input Voltage $\dots \dots \dots$ |

| Output Voltage Swing $\dots -0.3$ V to V <sub>DD</sub> + 0.3 V                                                                    |

| Operating Temperature Range (Ambient)40°C to +85°C                                                                                |

| Storage Temperature Range65°C to +150°C                                                                                           |

| Lead Temperature (5 sec) TQFP 280°C                                                                                               |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

DataSheet4U.com

#### **ENVIRONMENTAL CONDITIONS**

Ambient Temperature Rating:

$T_{AMB} = T_{CASE} - (PD \times \theta_{CA})$  $T_{CASE} = Case Temperature in °C$

PD = Power Dissipation in W

$\theta_{IA}$  = Thermal Resistance (Junction-to-Ambient)

$\theta_{JC}$  = Thermal Resistance (Junction-to-Case)

$\theta_{CA}$  = Thermal Resistance (Case-to-Ambient)

| Package | θ <sub>JA</sub> | θ <sub>JC</sub> | θ <sub>CA</sub> |

|---------|-----------------|-----------------|-----------------|

| TQFP    | 50°C/W          | 2°C/W           | 48°C/W          |

#### ADSST-73360AR (ADC)

#### **FEATURES**

Six 16-Bit A/D Converters Programmable Input Sample Rate Simultaneous Sampling 76 dB SNR 64 kS/s Maximum Sample Rate -83 dB Crosstalk Low Group Delay (125 μs Typ per ADC Channel) Programmable Input Gain Flexible Serial Port which Allows Multiple Devices to be Connected in Cascade Single (2.7 V to 5.5 V) Supply Operation 80 mW Max Power Consumption at 2.7 V On-Chip Reference 28-Lead SOIC

#### GENERAL DESCRIPTION

The ADSST-73360AR is a six-input channel analog front-end processor for power metering. It features six 16-bit A/D conversion provide 76 dB signal-to-noise ratio over a dc to 4 kHz signal bandwidth. Each channel also features a programmable input gain amplifier (PGA) with gain settings in eight stages from 0 dB to 38 dB.

The ADSST-73360AR is particularly suitable for industrial power metering as each channel samples synchronously, ensuring that there is no (phase) delay between the conversions. The ADSST-73360AR also features low group delay conversions on all channels.

An on-chip reference voltage is included with a nominal value of 1.2 V.

The sampling rate of the device is programmable with four separate settings offering 64 kHz, 32 kHz, 16 kHz, and 8 kHz sampling rates (from a master clock of 16.384 MHz).

A serial port (SPORT) allows easy interfacing of single or cascaded devices to industry standard DSP engines. The SPORT transfer rate is programmable to allow interfacing to both fast and slow DSP engines.

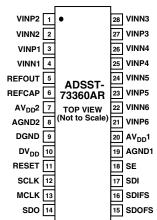

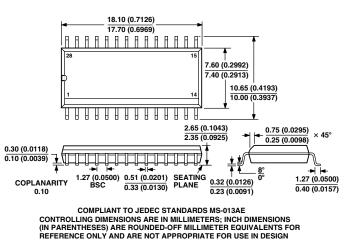

The ADSST-73360AR is available in 28-lead SOIC.

Figure 4. Functional Block Diagram

DataShe

## SPECIFICATIONS Adsst-73360ar

$(AVDD = 5 V \pm 10\%; DVDD = 5 V \pm 10\%; DGND = AGND = 0 V, f_{MCLK} = 16.384 \text{ MHz}, f_{SCLK} = 8.192 \text{ MHz}, f_S = 8 \text{ kHz}; T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted}^1.)$

| Parameter                                                         | Min | Тур             | Max   | Unit                    | Test Conditions/Comments                                        |      |

|-------------------------------------------------------------------|-----|-----------------|-------|-------------------------|-----------------------------------------------------------------|------|

| REFERENCE                                                         |     |                 |       |                         |                                                                 |      |

| REFCAP                                                            |     |                 |       |                         |                                                                 |      |

| Absolute Voltage, V <sub>REFCAP</sub>                             |     | 1.25            |       | V                       | 5  VEN = 0                                                      |      |

|                                                                   |     | 2.5             |       | V                       | 5  VEN = 1                                                      |      |

| REFCAP TC                                                         |     | 50              |       | ppm/°C                  | 0.1 µF Capacitor Required from, REFCAP to AGND2                 |      |

| REFOUT                                                            |     |                 |       |                         |                                                                 |      |

| Typical Output Impedance                                          |     | 130             |       | Ω                       |                                                                 |      |

| Absolute Voltage, V <sub>REFOUT</sub>                             |     | 1.25            |       | V                       | 5  VEN = 0, Unloaded                                            |      |

|                                                                   |     | 2.5             |       | V                       | 5  VEN = 1, Unloaded                                            |      |

| Minimum Load Resistance                                           | 2   |                 |       | kΩ                      | 5  VEN = 1                                                      |      |

| Maximum Load Capacitance                                          |     |                 | 100   | pF                      |                                                                 |      |

| ADC SPECIFICATIONS                                                |     |                 |       |                         |                                                                 |      |

| Maximum Input Range at VIN <sup>2, 3</sup>                        |     | 3.156           |       | V p-p                   | 5  VEN = 1, Measured Differentially                             |      |

| I G                                                               |     | 3.17            |       | dBm                     |                                                                 |      |

| Nominal Reference Level at VIN                                    |     | 2.1908          |       | V p-p                   | 5  VEN = 1, Measured Differentially                             |      |

| (0 dBm0)                                                          |     | 0               |       | dBm                     | ,,, ~ ~ ~ ~ ~ ~ ~ ~ ~                                           |      |

| Absolute Gain                                                     |     | 0               |       |                         |                                                                 |      |

| PGA = 0 dB                                                        |     | +0.1            |       | dB                      | 1.0 kHz                                                         |      |

| PGA = 38 dB                                                       |     | -0.5            |       | dB                      | 1.0 kHz                                                         |      |

| Gain Tracking Error                                               |     | $\pm 0.1$       |       | dB                      | 1.0  kHz, +3 dBm0 to -50 dBm0                                   | Dete |

| Signal to (Noise + Distortion)                                    |     |                 |       |                         | , · · · · · · · · · · · · · · · · ·                             | Data |

| PGA = 0 dB                                                        |     | 76              |       | dB                      | 0 Hz to $f_{s}/2$ ; $f_{s} = 8 \text{ kHz}$                     |      |

| PGA = 38 dB                                                       |     | 70              | DataS | heed U.com              | $0 \text{ Hz to } 4 \text{ kHz}; f_{\text{S}} = 64 \text{ kHz}$ |      |

| Total Harmonic Distortion                                         |     | 10              |       | ub                      |                                                                 |      |

| PGA = 0 dB                                                        |     | -86             |       | dB                      |                                                                 |      |

| PGA = 38  dB                                                      |     | -80             |       | dB                      |                                                                 |      |

| Intermodulation Distortion                                        |     | -79             |       | dB                      | PGA = 0 dB                                                      |      |

| Idle Channel Noise                                                |     | -76             |       | dB                      | PGA = 0 dB                                                      |      |

| Crosstalk ADC-to-ADC                                              |     | -85             |       | dB                      | ADC1 Input Signal Level: 1 kHz, 0 dBm0                          |      |

| Clossial IDC-10-IDC                                               |     | -05             |       | dD                      | ADC2 Input at Idle                                              |      |

| DC Offset                                                         |     | 20              |       | mV                      | PGA = 0 dB                                                      |      |

| Power Supply Rejection                                            |     | -55             |       | dB                      | Input Signal Level at AVDD and DVDD                             |      |

| Tower Suppry Rejection                                            |     |                 |       | dD                      | Pins 1.0 kHz, 100 mV p-p Sine                                   |      |

| Wave Group Delay <sup>4, 5</sup>                                  |     | 25              |       | μs                      | 64 kHz Output Sample Rate                                       |      |

| wave Group Delay                                                  |     | 50              |       | μs<br>μs                | 32 kHz Output Sample Rate                                       |      |

|                                                                   |     | 95              |       | μs<br>μs                | 16 kHz Output Sample Rate                                       |      |

|                                                                   |     | 190             |       | μs<br>μs                | 8 kHz Output Sample Rate                                        |      |

| Input Resistance at VIN <sup>2, 4</sup>                           |     | 25              |       | $\mu s$<br>k $\Omega^6$ | DMCLK = 16.384 MHz                                              |      |

| •                                                                 |     |                 |       |                         |                                                                 |      |

| FREQUENCY RESPONSE                                                |     |                 |       |                         |                                                                 |      |

| (ADC) <sup>7</sup> Typical Output<br>Frequency (Normalized to f.) |     |                 |       |                         |                                                                 |      |

| Frequency (Normalized to f <sub>S</sub> )<br>0                    |     | 0               |       | dB                      |                                                                 |      |

| 0.03125                                                           |     | -0.1            |       | dB<br>dB                |                                                                 |      |

|                                                                   |     |                 |       | dB<br>dB                |                                                                 |      |

| 0.0625<br>0.125                                                   |     | $-0.25 \\ -0.6$ |       | dB<br>dB                |                                                                 |      |

|                                                                   |     |                 |       | dB<br>dB                |                                                                 |      |

| 0.1875                                                            |     | -1.4            |       |                         |                                                                 |      |

| 0.25                                                              |     | -2.8            |       | dB                      |                                                                 |      |

| 0.3125                                                            |     | -4.5            |       | dB                      |                                                                 |      |

| 0.375                                                             |     | -7.0            |       | dB                      |                                                                 |      |

| 0.4375                                                            |     | -9.5            | _     | dB                      |                                                                 |      |

| > 0.5                                                             |     | < -12.5         | )     | dB                      |                                                                 |      |

DataSheet4U.com

et4U.com

| Parameter                             | Min                  | Тур  | Max      | Unit | Test Conditions/Comments  |

|---------------------------------------|----------------------|------|----------|------|---------------------------|

| LOGIC INPUTS                          |                      |      |          |      |                           |

| V <sub>INH</sub> , Input High Voltage | $V_{DD} - 0.$        | 8    | $V_{DD}$ | V    |                           |

| V <sub>INL</sub> , Input Low Voltage  | 0                    |      | 0.8      | V    |                           |

| I <sub>IH</sub> , Input Current       |                      | -0.5 |          | μA   |                           |

| C <sub>IN</sub> , Input Capacitance   |                      | 10   |          | pF   |                           |

| LOGIC OUTPUT                          |                      |      |          |      |                           |

| V <sub>OH</sub> , Output High Voltage | V <sub>DD</sub> - 0. | 4    | $V_{DD}$ | V    | $ IOUT  \leq 100 \ \mu A$ |

| V <sub>OL</sub> , Output Low Voltage  | 0                    |      | 0.4      | V    | $ IOUT  \leq 100 \ \mu A$ |

| Three-State Leakage Current           |                      | -0.3 |          | μA   |                           |

| POWER SUPPLIES                        |                      |      |          |      |                           |

| $AV_{DD}1$ , $AV_{DD}2$               | 4.5                  |      | 5.5      | V    |                           |

| $DV_{DD}$                             | 4.5                  |      | 5.5      | V    |                           |

| I <sub>DD</sub> <sup>8</sup>          |                      |      |          |      | See Table II              |

NOTES

<sup>1</sup>Operating temperature range is as follows:  $-40^{\circ}$ C to  $+85^{\circ}$ C. Therefore,  $T_{MIN} = -40^{\circ}$ C and  $T_{MAX} = +85^{\circ}$ C.

<sup>2</sup>Test conditions: Input PGA set for 0 dB gain (unless otherwise noted).

<sup>3</sup>At input to sigma-delta modulator of ADC.

<sup>4</sup>Guaranteed by design.

<sup>5</sup>Overall group delay will be affected by the sample rate and the external digital filtering.

<sup>6</sup>The ADCs input impedance is inversely proportional to DMCLK and is approximated by: (4 ~10")/DMCLK.

<sup>7</sup>Frequency response of ADC measured with input at audio reference level (the input level that produces an output level of -10 dBm0), with 38 dB preamplifier bypassed and input gain of 0 dB.

<sup>8</sup>Test Conditions: no load on digital inputs, analog inputs ac coupled to ground.

Specifications subject to change without notice.

#### et4U.con

Table II. Current Summary ( $AV_{DD} = DV_{DD} = 3.3 V$ )

DataShe

| Conditions                | Analog<br>Current | Digital <sub>Da</sub><br>Current | taTotal t4U.com<br>Current (Max) | SE | MCLKON<br>ON | Comments                                                |

|---------------------------|-------------------|----------------------------------|----------------------------------|----|--------------|---------------------------------------------------------|

| ADCs Only On              | 16                | 16                               | 32                               | 1  | YES          | <b>REFOUT</b> Disabled                                  |

| REFCAP Only On            | 0.8               | 0                                | 0.8                              | 0  | NO           | REFOUT Disabled                                         |

| REFCAP and REFOUT Only On | 3.5               | 0                                | 3.5                              | 0  | NO           |                                                         |

| All Sections Off          | 0.1               | 1.9                              | 2.0                              | 0  | YES          | MCLK Active Levels<br>Equal to 0 V and DV <sub>DD</sub> |

| All Sections Off          | 0                 | 0.05                             | 0.06                             | 0  | NO           | Digital Inputs Static and Equal to 0 V and $DV_{DD}$    |

#### **ABSOLUTE MAXIMUM RATINGS\***

| $(T_A = 25^{\circ}C \text{ unless otherwise noted.})$                  |

|------------------------------------------------------------------------|

| $AV_{DD}$ , $DV_{DD}$ to $GND$                                         |

| AGND to DGND                                                           |

| Digital I/O Voltage to DGND $\dots -0.3$ V to DV <sub>DD</sub> + 0.3 V |

| Analog I/O Voltage to AGND $\dots -0.3$ V to AV <sub>DD</sub> + 0.3 V  |

| Operating Temperature Range Industrial (A Version)                     |

| 40°C to +85°C                                                          |

| Storage Temperature Range                                              |

| Maximum Junction Temperature 150°C    |

|---------------------------------------|

| SOIC, $\theta_{JA}$ Thermal Impedance |

| Lead Temperature, Soldering           |

| Vapor Phase (60 sec)                  |

| Infrared (15 sec) 220°C               |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADSST-EM-3035 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

#### PIN CONFIGURATION

#### PIN FUNCTION DESCRIPTIONS

| Mnemonic           | Function                                                                                                                                                                                                        | Mnemonic           | Function                                                                                                                                                                                                                               |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VINP1              | Analog Input to the Positive Terminal of Input<br>Channel 1                                                                                                                                                     | RESET              | Active Low Reset Signal. This input resets the entire chip, resetting the control registers and clearing the digital                                                                                                                   |

| VINN1              | Analog Input to the Negative Terminal of Input<br>Channel 1                                                                                                                                                     | SCLK               | circuitry. Output Serial Clock whose rate determines the serial trans-                                                                                                                                                                 |

| VINP2              | Analog Input to the Positive Terminal of Input<br>Channel 2                                                                                                                                                     |                    | fer rate to/from the ADSST73360AR. It is used to clock<br>data or control information to and from the serial port<br>(SPORT). The frequency of SCLK is equal to the frequency                                                          |

| VINN2              | Analog Input to the Negative Terminal of Input<br>Channel 2                                                                                                                                                     |                    | of the master clock (MCLK) divided by an integer number<br>This integer number being the product of the external<br>master clock rate divider and the serial clock rate divider.                                                       |

| VINP3              | Analog Input to the Positive Terminal of InputaShee<br>Channel 3                                                                                                                                                | t4U-com<br>MCLK    | Master Clock rate divider and the serial clock rate divider.<br>Master Clock Input. MCLK is driven from an external clock signal.                                                                                                      |

| VINN3              | Analog Input to the Negative Terminal of Input<br>Channel 3                                                                                                                                                     | SDO                | Serial Data Output of the ADSST-73360AR. Both data                                                                                                                                                                                     |

| VINP4              | Analog Input to the Positive Terminal of Input<br>Channel 4                                                                                                                                                     |                    | and control information may be output on this pin and are<br>clocked on the positive edge of SCLK. SDO is in three-<br>state when no information is being transmitted and when                                                         |

| VINN4              | Analog Input to the Negative Terminal of Input<br>Channel 4                                                                                                                                                     | SDOFS              | SE is low.<br>Framing Signal Output for SDO Serial Transfers. The                                                                                                                                                                      |

| VINP5              | Analog Input to the Positive Terminal of Input<br>Channel 5                                                                                                                                                     |                    | frame sync is one bit wide and it is active one SCLK period<br>before the first bit (MSB) of each output word. SDOFS<br>is referenced to the positive edge of SCLK. SDOFS is                                                           |

| VINN5              | Analog Input to the Negative Terminal of Input<br>Channel 5                                                                                                                                                     |                    | in three-state when SE is low.                                                                                                                                                                                                         |

| VINP6              | Analog Input to the Positive Terminal of Input<br>Channel 6                                                                                                                                                     | SDIFS              | Framing Signal Input for SDI Serial Transfers. The frame<br>sync is one bit wide and it is valid one SCLK period<br>before the first bit (MSB) of each input word. SDIFS is                                                            |

| VINN6              | Analog Input to the Negative Terminal of Input<br>Channel 6                                                                                                                                                     |                    | sampled on the negative edge of SCLK and is ignored when SE is low.                                                                                                                                                                    |

| REFOUT             | Buffered Reference Output, which has a nominal value<br>of 1.2 V or 2.4 V, the value being dependent on the<br>status of Bit 5 VEN (CRC:7). This pin can be overdriven<br>by an external reference if required. | SDI                | Serial Data Input of the ADSST-73360AR. Both data<br>and control information may be input on this pin and are<br>clocked on the negative edge of SCLK. SDI is ignored<br>when SE is low.                                               |

| REFCAP             | A Bypass Capacitor to AGND2 of 0.1 µF is required<br>for the on-chip reference. The capacitor should be<br>fixed to this pin.                                                                                   | SE                 | SPORT Enable. Asynchronous input enable pin for the<br>SPORT. When SE is set low by the DSP, the output pins<br>of the SPORT are three-stated and the input pins are<br>ignored. SCLK is also disabled internally in order to decrease |

| AV <sub>DD</sub> 2 | Analog Power Supply Connection                                                                                                                                                                                  |                    | power dissipation. When SE is brought high, the control<br>and data registers of the SPORT are at their original values                                                                                                                |

| AGND2              | Analog Ground/Substrate Connection                                                                                                                                                                              |                    | (before SE was brought low. However, the timing counters                                                                                                                                                                               |

| DGND               | Digital Ground/Substrate Connection                                                                                                                                                                             |                    | and other internal registers are at their reset values.                                                                                                                                                                                |

| DV <sub>DD</sub>   | Digital Power Supply Connection                                                                                                                                                                                 | AGND1              | Analog Ground Connection                                                                                                                                                                                                               |

| J.com              |                                                                                                                                                                                                                 | AV <sub>DD</sub> 1 | Analog Power Supply Connection www.DataSheet4U.                                                                                                                                                                                        |

DataSheet4U.com

et4U.com

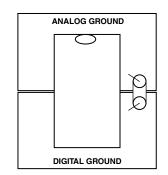

#### **Grounding and Layout**

#### Figure 5. Grounding and Layout

Since the analog inputs to the ADSST-73360AR are differential, most of the voltages in the analog modulator are common-mode voltages. The excellent common-mode rejection of the part will remove common-mode noise on these inputs. The analog and digital supplies of the ADSST-73360AR are independent and separately pinned out to minimize coupling between analog and digital sections of the device. The digital filters on the encoder section will provide rejection of broadband noise on the power supplies, except at integer multiples of the modulator sampling frequency. The digital filters also remove noise from the analog inputs provided the noise source does not saturate the analog modulator. However, because the resolution of the ADSST-73360LAR ADC is high, and the noise levels from the ADSST-73360AR are so low, care must be taken with regard to grounding and layout.

> The printed circuit board that houses the ADSST-73360AR should be designed so the analog and digital sections are separated and confined to certain sections of the board. The ADSST-73360AR pin configuration offers a major advantage in that its analog and digital interfaces are connected on opposite sides of the package. This facilitates the use of ground planes that can be easily separated, as shown in Figure 5. A minimum etch technique is generally best for ground planes as it gives the best shielding. Digital and analog ground planes should be joined in only one place. If this connection is close to the device, it is recommended to use a ferrite bead inductor as shown in Figure 5.

> Avoid running digital lines under the device for they will couple noise onto the die. The analog ground plane should be allowed to run under the ADSST-73360AR to avoid noise coupling. The power supply lines to the ADSST-73360AR should use as large a trace as possible to provide low impedance paths and reduce the effects of glitches on the power supply lines. Fast switching signals such as clocks should be shielded with digital ground to avoid radiating noise to other sections of the board, and clock signals should never be run near the analog inputs. Traces on opposite sides of the board should run at right angles to each other. This will reduce the effects of feedthrough through the board. A micro-strip technique is by far the best but is not always possible with a double-sided board. In this technique, the component side of the board is dedicated to ground planes while signals are placed on the other side.

Good decoupling is important when using high speed devices. All analog and digital supplies should be decoupled to AGND DataSheet4U.com and DGND respectively, with 0.1  $\mu$ F ceramic capacitors in parallel with 10  $\mu$ F tantalum capacitors. To achieve the best from these decoupling capacitors, they should be placed as close as possible to the device, ideally right up against it. In systems where a common supply voltage drives both the AVDD and DVDD of the ADSST-73360AR, it is recommended that the system's AVDD supply be used. This supply should have the recommended analog supply decoupling between the AVDD pins of the ADSST-73360AR and AGND and the recommended digital supply decoupling capacitors between the DVDD pin and DGND.

## NOTE: FOR MORE DETAILS ON ADSST-73360AR, PLEASE REFER TO DATA SHEET OF AD73360

#### Interfaces between ADSST-EM-3035 and Microcontroller Overview

The following paragraphs describe the interface between the ADSST-EM-3035 chipset and the microcontroller. The sequence of operations is a critical issue for proper functioning of the two processors on the board. The DSP processor is primarily used to compute various parameters, provide the impulse outputs on the external LEDs and provide automatic gain switching inside the ADC. The microcontroller can collect the data from the chipset for data management for further processing. There are two basic functions that the microcontroller performs in a handshaking mode with the DSP processor:

• Boot loading the DSP with metering software on power up (for non-ROM coded version only)

• Communication with the DSP on SPI to: DataSheet4U.com

Send Initialization data on power up after boot loading the DSP with metering software

- Receive data from DSP during normal operation

- Receive and send data during calibration

#### This section describes the Boot loading and SPI operations.

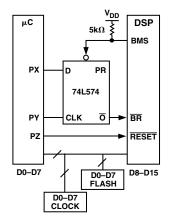

## BOOT LOADING THE DSP PROCESSOR FROM THE MICROCONTROLLER

The DSP processor has an internal program memory RAM that supports boot loading. With boot loading, the processor reads instructions from a byte-wide data bus connected to the microcontroller and stores the instructions in the 24-bit wide internal program memory. The host microcontroller, is the source of bytes to be loaded into on-chip memory. The choice of which technique to use depends upon the I/O structure of the host microcontroller, availability of I/O port lines, and the amount of address decoding logic already available in the system. The description here is one of the many ways that this could be configured. However, the software on the microcontroller has been written in way to make optimum use of the configuration.

Figure 6 illustrates the system implementation to allow a microcontroller to boot the DSP processor. The only hardware required is a D-type flip-flop and a 5 k $\Omega$  resistor. The resistor is used to pull the DSP processor's BMS pin (Boot Memory Select) high.

The DSP processor boots using the BDMA option. The BDMA option can be used when pins Mode A, Mode B, and Mode C on the DSP are tied low. With these pins tied low the DSP automatically enters its boot sequence after the processor is reset. In the sequence of booting the DSP, it has to be loaded with an object code into the internal program memory. The byte wide memory boot code file has the following structure:

- a) 32 words or 96 bytes of the initial header,

- b)81 words or 243 bytes for initializing BDMA and associated registers,

- c) 6712 words or 20136 bytes of program code.

#### Figure 6. System Architecture for Boot Loading DSP Processor From Microcontroller

et4U.com

When the DSP is reset with the pins Mode A, Mode B, and Mode C tied low, it enters into the byte wide memory data access mode. The boot loading process will consist of the DSP reading the first 32 words, a small delay, say one millisecond foret4 it execute these 32 words of program. The DSP will then read the next 81 words. After which a small delay, of say one millisecond, will be required for it to execute these 81 words. The DSP will now (with BDMA registers initialized) read the code length also initialized in the previous process. It should be noted that when the DSP reads the 20136 bytes from its port of the

program code, it will overwrite the first 113 words (i.e., 339 bytes). After reading 20136 bytes, it will start execution automatically.

The process of loading the code to the DSP is as follows:

- After the microcontroller is reset, hold DSP in reset by bringing reset pin low.

- Make PX high and clock PY (low to high transition). This will make BR low. In effect, the DSP will not read because it has granted its buses since BR is asserted.

- Put the first byte of the program code on the DSP bus D8 to D15 and deassert BR, which is done by taking PX low and clocking a transition on PY (low to high). Since the DSP buses have been released, it will read the byte and assert BMS. The assertion of BMS will cause the flip-flop to preset (PR on 74LS74) itself and therefore BR is again asserted.

- Continue this process byte by byte for 96 bytes and give a small delay.

- After the delay continue the byte loading process for the next 243 bytes and give a small delay again.

- Continue the byte loading process for 20136 bytes.

- Soon after the last program byte is loaded, the DSP starts execution of the code.

At the start of execution, the DSP waits for uploading of 154 bytes of data consisting of calibration constants (gain & dc offsets), E-pulse constants and filter coefficients. This data has to be sent\_ataShe to the DSP processor on the SPI port. Until the DSP receives the 154 bytes, the actual process of executing the metering code on the DSP does not start. Soon after receiving all the constants (i.e. 154 bytes) the metering process starts. Four dummy bytes have to be sent after the start of execution for the DSP to send back the check sum of its internal code. The microcontroller can use this to verify that the complete metering code has been loaded on the DSP processor properly. The DSP is now ready to provide the computed data on the SPI port.

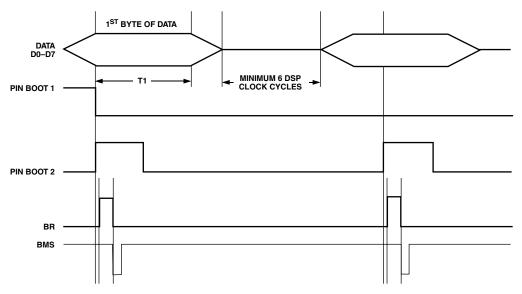

Figure 7. Timing Diagram for Boot Loading the DSP Processor

DataSheet4U.com

#### SERIAL PERIPHERAL INTERFACE (SPI) AND CONTROL

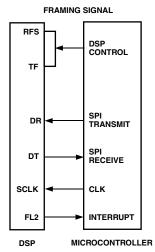

The DSP and the microcontroller are interfaced through Serial Peripheral Interface (SPI). The microcontroller is always configured as a master and the DSP as a slave.

Figure 8. Serial Peripheral Interface and Control

#### **SPI OPERATION**

There are two modes of communication between DSP and microcontroller.

Microcontroller to DSP (while uploading the initial data of 154 bytes, including four bytes to read checksum of code from DSP, and sending a command)

Bring the DSP\_control pin low, i.e., give a high to low transition. This informs the DSP that the data after this transition is a valid data.

Send the data byte on the microcontroller's SPI port. Since the microcontroller is configured as a master, the clock signal will be generated by the microcontroller and the DSP being a slave will read the data byte in sync with the clock signal. Bring DSP\_control signal back to high state.

• DSP to Microcontroller (while transmitting computed data to the microcontroller)

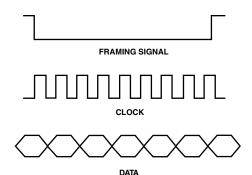

The DSP during its metering code execution, is ready to give the computed parameters to the microcontroller after every 32 cycles of power line.

To request data from the DSP, the microcontroller sends a request code 45h on the SPI bus.

The DSP then sends a high to low transition on Pin FL2 soon after it completes the next 32 cycles of computation as an indication to the microcontroller that it is ready to transmit most recent data.

Since the microcontroller is a master, it has to now send clock signal to the DSP on the SPI to receive data. For the clock signal to be generated, the microcontroller has to send a dummy byte. The dummy byte (say, 0xFF) should be one that is not recognized by the DSP as a command. The microcontroller may send as many dummy bytes as it requires up to a maximum of 522 bytes for the complete

DataSheet4U.com

data train. The data received from the DSP will be in the same sequence as described in Table IV. If the microcontroller does not require all the parameters then it may stop sending dummy bytes at any time.

The diagram below shows the sequence of operation.

Figure 9. SPI Sequence of Operation

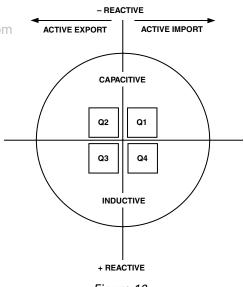

#### **Quadrant and Other Conventions**

The data sent by the DSP is based on the following convention:

- Figure 10 gives the quadrant convention used by the chipset.

- Import means delivered from the utility to the user.

- Export means delivered by the user to the utility.

- Total means total of all three phases.

Figure 10.

#### **Power Up Initialization**