A brief introduction to the development of DDR memory

The primary function of memory is to store programs and a variety of data, and to automatically complete the access of programs or data at high speed in the computer operating.

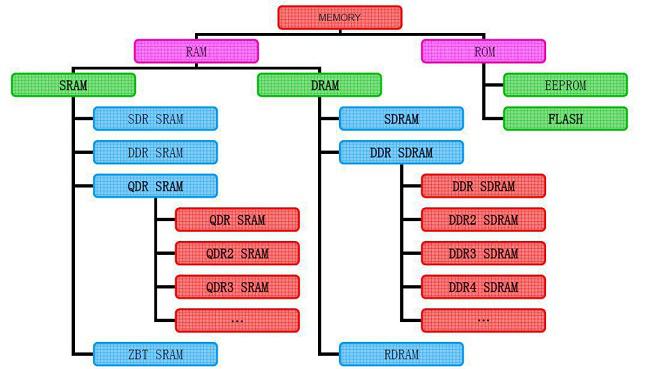

1. Conceptual understanding of ROM and RAM

ROM: Read-only memory. The data stored in ROM is generally written in advance before being loaded into the machine, different from RAM that can be quickly and conveniently rewritten. The data stored in ROM is stable, even in the case of power off.

RAM (random access memory) can be divided into SRAM (static random access memory) and DRAM (dynamic random access memory).

SRAM (static random access memory), is a memory with static access that saves the data internally without refreshing the circuit. The advantage is that its speed is fast, and it does not have to cooperate with the memory refresh circuit, which can improve overall efficiency. But disadvantages are low integration and large power consumption. Even with the same capacity, bigger it is, higher price it has. A small amount is used in critical systems to improve efficiency.

DRAM (dynamic random access memory) is the most common system memory with keeping data for a short time. In order to maintain data, DRAM uses capacitive storage, so it must be refreshed once a time. If the storage unit is not refreshed, the stored information will be lost.

SDRAM (synchronous dynamic random access memory), is a kind of DRAM, which is developed on the basis of DRAM. Synchronization means memory needs to synchronize the clock when it works. Both the transmission of internal commands and the data are based on the clock. Dynamics refers to that storage array needs constant refreshment to prevent data from being lost. Random means that the data is not stored in a linear order, but read and written by a specified address.

DDR SDRAM is also developed on the basis of SDRAM. This improved DRAM is basically as same as SDRAM, while DDR SDRAM can read and write data twice in a clock, leading to double the speed of data transmission. This is the most widely used memory in the computer today, and it has cost advantages.

2. Introduction to the development of SDRAM

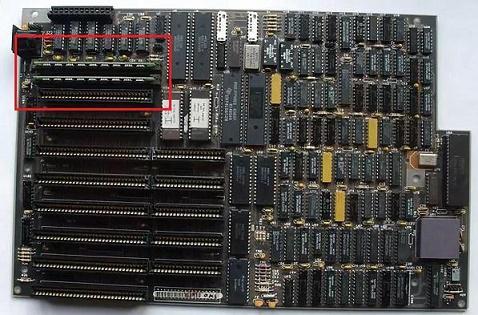

There is no memory bar in the original PC. Memory in the form of DIP chips is installed directly on the motherboard's DRAM socket. Its capacity is only 64KB to 256KB by installing 8 to 9 such chips. It is very difficult to expand its capacity when this was enough for the processors and the programs at that time. Until the emergence of 80286, both hardware and software are eager for larger memory. The memory on the motherboard can no longer meet the requirements, so memory bar is born.

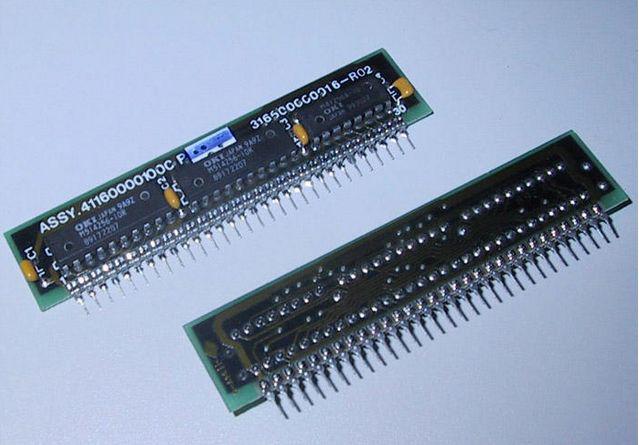

The previous 30pin SIPP (Single in-line Pin Package) interface was quickly replaced by SIMM (Single in-line Memory modules), although their definition of the pin is similar, that is to say both sides of the golden finger transmit same data. Early memory frequency isn’t synchronous with CPU external frequency, namely asynchronous DRAM. Asynchronous DRAM can be divided into FPM DRAM (Fast page mode DRAM) and EDO DRAM (Extended data out DRAM). Common interfaces are 30pin SIMM and 72pin SIMM, both of which are working at 5V voltage.

Interestingly, DIP chips and memory bar have coexisted for a long time and they can work together. For example, on many 286 motherboards, you can see slots of both DIP and 30pin SIMM memory.

Subsequently, 72pin SIMM memory have emerged with a single memory data bus of 32 bit. One can satisfy the 32-bit data bus processor while Pentium processor with 64-bit data bus needs two. Because of its increasing memory capacity, it quickly replaced 30pin SIMM memory. So, most processors such as 386, 486, Pentium, Pentium Pro, and early Pentium II use this memory.

(1) FPM DRAM (Fast page mode DRAM)

FPM DRAM has 30pin SIMM and 72pin SIMM, the former common on 286, 386 and 486 PCs, the latter common on 486 and earlier Pentium computers. The common capacity of 30pin SIMM is 256kb, while 72pin SIMM is from 512KB to 2MB.

(2) EDO DRAM (Extended data out DRAM)

EDO DRAM is a kind of 72pin SIMM that has larger capacity and a more advanced addressing mode. This memory simplifies the fluency of data access contributing to read