## **AWT6222**

US Cellular/Japan Cellular/IMT

UMTS/WCDMA Linear Power Amplifier Module Data Sheet - Rev 2.1

- **FEATURES** InGaP HBT Technology

- High Efficiency: 22 % @ +16 dBm Роит (without DC/DC converter) 40 % @ maximum Pout

- Low Quiescent Current: 8 mA

- Internal Voltage Regulation

- Common VMODE Control Line

- Simplified Vcc Bus PCB routing

- Reduced External Component Count

- Low Profile Surface Mount Package: 1 mm

- **HSDPA** Compliant

- RoHS Compliant Package, 250 °C MSL-3

## **APPLICATIONS**

WCDMA/HSPA JCell/IMT Dual-Band Wireless Handsets and Data Devices

## PRODUCT DESCRIPTION

The AWT6222 addresses the demand for increased integration in dual-band handsets for cellular network deployments. The small footprint 3 mm x 5 mm x 1 mm surface mount RoHS compliant package contains independent RF PA paths to ensure optimal performance in both frequency bands, while achieving a 25% PCB space savings compared with solutions requiring two single-band PAs. The package pinout was chosen to enable handset manufacturers to easily route Vcc to both power amplifiers and simplify control with a common VMODE pin. The device is manufactured on an advanced InGaP HBT MMIC technology offering state-of-the-art reliability, temperature stability, and ruggedness. The AWT6222 incorporates ANADIGICS' HELP3™ technology to provide low power consumption without the need for an external voltage regulator. Two operating modes provide optimum efficiency at high and medium/low power output levels, thereby dramatically increasing handset talk-time and standby-time. Its built-in voltage regulator eliminates the need for external voltage regulation and load switches. The 3 mm x 5 mm x 1 mm surface mount package incorporates matching networks optimized for output power, efficiency and linearity in a 50  $\Omega$  system.

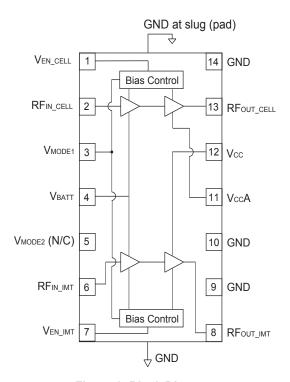

Figure 1: Block Diagram www.DataSheet4U.com

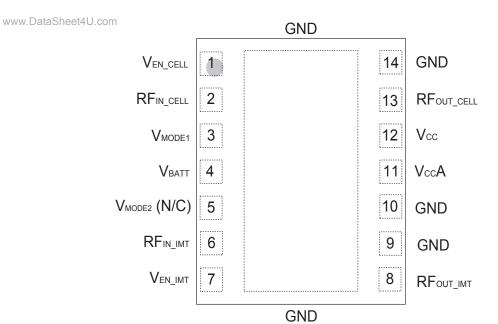

Figure 2: Pinout

**Table 1: Pin Description**

| PIN | NAME                     | DESCRIPTION                   |

|-----|--------------------------|-------------------------------|

| 1   | V <sub>EN_CELL</sub>     | Enable Voltage for Cell Bands |

| 2   | RF <sub>IN_CELL</sub>    | RF Input for Cell Bands       |

| 3   | V <sub>MODE1</sub>       | Mode Control Voltage 1        |

| 4   | $V_{BATT}$               | Battery Voltage               |

| 5   | V <sub>MODE2</sub> (N/C) | No Connection                 |

| 6   | RF <sub>IN_IMT</sub>     | RF Input for IMT Band         |

| 7   | V <sub>EN_IMT</sub>      | Enable Voltage for IMT Band   |

| 8   | RFout_IMT                | RF Output for IMT Band        |

| 9   | GND                      | Ground                        |

| 10  | GND                      | Ground                        |

| 11  | VccA                     | Supply Voltage A              |

| 12  | Vcc                      | Supply Voltage                |

| 13  | RFOUT_CELL               | RF Output for Cell Band       |

| 14  | GND                      | Ground                        |

## **ELECTRICAL CHARACTERISTICS**

www.DataSheet4U.com

**Table 2: Absolute Minimum and Maximum Ratings**

| PARAMETER                          | MIN | MAX  | UNIT |

|------------------------------------|-----|------|------|

| Supply Voltage (VBATT, Vcc, VccA)  | 0   | +5   | V    |

| Mode Control Voltage (VMODE)       | 0   | +3.5 | V    |

| Enable Voltage (VEN_CELL, VEN_IMT) | 0   | +3.5 | ٧    |

| RF Input Power (Pℕ)                | -   | +10  | dBm  |

| Storage Temperature (Tstg)         | -40 | +150 | °C   |

Stresses in excess of the absolute ratings may cause permanent damage. Functional operation is not implied under these conditions. Exposure to absolute ratings for extended periods of time may adversely affect reliability.

**Table 3: Operating Ranges**

| PARAMETER                                                                                                | MIN                                                                                      | TYP                      | MAX                      | UNIT | COMMENTS                                  |

|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------|--------------------------|------|-------------------------------------------|

| Operating Frequency (f)                                                                                  | 824<br>1920                                                                              | -                        | 849<br>1980              | MHz  | Japan and US Cellular<br>IMT              |

| Supply Voltage (Vcc and Vbatt)                                                                           | +3.2                                                                                     | +3.4                     | +4.2                     | V    |                                           |

| Enable Voltage (V <sub>EN</sub> )                                                                        | +2.2<br>0                                                                                | +2.4<br>-                | +3.1<br>+0.5             | V    | PA "on"<br>PA "shut down"                 |

| Mode Control Voltage (V <sub>MODE</sub> )                                                                | +2.2<br>0                                                                                | +2.4                     | +3.1<br>+0.5             | V    | Low Bias Mode<br>High Bias Mode           |

| Cellular RF Output Power (Pout) R99 WCDMA, HPM HSPA (MPR=0), HPM R99 WCDMA, LPM HSPA (MPR=0), LPM        | 28.5 <sup>(1)</sup><br>27.5 <sup>(1)</sup><br>15.5 <sup>(1)</sup><br>14.5 <sup>(1)</sup> | 29<br>28<br>16<br>15     | 29<br>28<br>16<br>15     | dBm  | 3GPP TS 34.121-1, Rel<br>7 Table C.11.1.3 |

| IMT RF Output Power (Pour)<br>R99 WCDMA, HPM<br>HSPA (MPR=0), HPM<br>R99 WCDMA, LPM<br>HSPA (MPR=0), LPM | 28 <sup>(1)</sup><br>27 <sup>(1)</sup><br>15.5 <sup>(1)</sup><br>14.5 <sup>(1)</sup>     | 28.5<br>27.5<br>16<br>15 | 28.5<br>27.5<br>16<br>15 | dBm  | 3GPP TS 34.121-1, Rel<br>7 Table C.11.1.3 |

| Case Temperature (Tc)                                                                                    | -30                                                                                      | -                        | +90                      | °C   |                                           |

The device may be operated safely over these conditions; however, parametric performance is guaranteed only over the conditions defined in the electrical specifications.

Notes:

(1) For operation at Vcc = +3.2 V, Pout is derated by 0.5 dB (all operating modes).

# Table 4: Electrical Specifications - Cellular Band ( $T_c$ = +25 °C, $V_{BATT}$ = $V_{CC}$ = +3.4 V, $V_{ENABLE}$ = +2.4 V, 50 $\Omega$ system)

| Nw.BataSheet4U.com                                            | nain:        | T)/D           | MAY            |        | COMMENTS                                                                   |                            |  |

|---------------------------------------------------------------|--------------|----------------|----------------|--------|----------------------------------------------------------------------------|----------------------------|--|

| PARAMETER                                                     | MIN          | TYP            | MAX            | UNIT   | Роит                                                                       | V <sub>MODE1</sub>         |  |

| Gain                                                          | 25.0<br>14.0 | 28<br>15.5     | 30.5<br>18.0   | dB     | +29 dBm<br>+16 dBm                                                         | 0 V<br>2.4 V               |  |

| ACLR1 at 5 MHz offset (1)                                     | -            | -41<br>-42     | -37.5<br>-37.5 | dBc    | +29 dBm<br>+16 dBm                                                         | 0 V<br>2.4 V               |  |

| ACLR2 at 10 MHz offset                                        | 1 1          | -62<br>-57     | -48<br>-48     | dBc    | +29 dBm<br>+16 dBm                                                         | 0 V<br>2.4 V               |  |

| Power-Added Efficiency (1)                                    | 37<br>19     | 41<br>22       | -              | %      | +29 dBm<br>+16 dBm                                                         | 0 V<br>2.4 V               |  |

| Quiescent Current (lcq)<br>Low Bias Mode                      | 1            | 8              | 13             | mA     | V <sub>MODE1</sub> = +2.4 V                                                |                            |  |

| Mode Control Current                                          | -            | 0.35           | 0.8            | mA     | through V <sub>MODE</sub> pins, V <sub>MODE</sub> = +2.                    |                            |  |

| Enable Current                                                | -            | 0.5            | 0.8            | mA     | through VENABLE                                                            | oin                        |  |

| BATT Current                                                  | -            | 3              | 5              | mA     | through VBATT pin,                                                         | V <sub>MODE1</sub> = 2.4 V |  |

| Leakage Current                                               | -            | <1             | 5              | μA     | V <sub>BATT</sub> = +4.3 V, V<br>V <sub>ENABLE</sub> = 0 V, V <sub>M</sub> |                            |  |

| Noise in Receive Band <sup>(2)</sup> (Band 6)                 | -            | -134.5<br>-139 | -133<br>-137   | dBm/Hz | P <sub>OUT</sub> = +29 dBm.<br>P <sub>OUT</sub> = +16 dBm.                 |                            |  |

| Noise in Receive Band <sup>(3)</sup> (Band 5)                 | 1 1          | -134.5<br>-139 | -133<br>-137   | dBm/Hz | Pout = +29 dBm<br>Pout = +16 dBm                                           |                            |  |

| Harmonics<br>2fo<br>3fo, 4fo                                  | 1 1          | -45<br>-50     | -30<br>-35     | dBc    | Роит <u>&lt;</u> +29 dBm                                                   |                            |  |

| Input Impedance                                               | -            | -              | 2:1            | VSWR   |                                                                            |                            |  |

| Spurious Output Level (all spurious outputs)                  | -            | -              | -70            | dBc    | See Note 4                                                                 |                            |  |

| Load mismatch stress with no permanent degradation or failure | 8:1          | -              | -              | VSWR   | Applies over full                                                          | operating range            |  |

## Notes:

<sup>(1)</sup> ACLR and Efficiency measured at 836.5 MHz.

<sup>(2) 875</sup> MHz to 885 MHz.

<sup>(3) 869</sup> MHz to 894 MHz.

<sup>(4)</sup> Pout < +29 dBm, In-band load VSWR < 5:1, Out-of-band load VSWR < 10:1. Applies over all operating conditions.

## Table 5: Electrical Specifications - IMT (Band 1) (Tc = +25 °C, VBATT = Vcc = +3.4 V, VENABLE = +2.4 V, 50 $\Omega$ system)

| ww.DataSheet4U.com                                            |            | TVD            | MAY          | LINUT  | COMMENTS                                                                   |                                                                 |

|---------------------------------------------------------------|------------|----------------|--------------|--------|----------------------------------------------------------------------------|-----------------------------------------------------------------|

| PARAMETER                                                     | MIN        | TYP            | MAX          | UNIT   | Роит                                                                       | V <sub>MODE1</sub>                                              |

| Gain                                                          | 25<br>12.0 | 27.5<br>14.0   | 30<br>16.0   | dB     | +28.5 dBm<br>+16 dBm                                                       | 0 V<br>2.4 V                                                    |

| ACLR1 at 5 MHz offset (1)                                     | -          | -41<br>-43     | -37.5<br>-38 | dBc    | +28.5 dBm<br>+16 dBm                                                       | 0 V<br>2.4 V                                                    |

| ACLR2 at 10 MHz offset                                        |            | -55<br>-56     | -48<br>-48   | dBc    | +28.5 dBm<br>+16 dBm                                                       | 0 V<br>2.4 V                                                    |

| Power-Added Efficiency (1)                                    | 36.5<br>19 | 40<br>23       | 1 1          | %      | +28.5 dBm<br>+16 dBm                                                       | 0 V<br>2.4 V                                                    |

| Quiescent Current (lcq)<br>Low Bias Mode                      | -          | 8              | 13           | mA     | V <sub>MODE1</sub> = +2.4 V                                                |                                                                 |

| Mode Control Current                                          | -          | 0.35           | 0.8          | mA     | through VMODE pin                                                          | s, V <sub>MODE</sub> = +2.4 V                                   |

| Enable Current                                                | -          | 0.3            | 0.8          | mA     | through VENABLE                                                            | oin                                                             |

| BATT Current                                                  | -          | 3              | 5            | mA     | through VBATT pin,                                                         | V <sub>MODE1</sub> = 2.4 V                                      |

| Leakage Current                                               | -          | <1             | 5            | μΑ     | V <sub>BATT</sub> = +4.3 V, V<br>V <sub>ENABLE</sub> = 0 V, V <sub>N</sub> |                                                                 |

| Noise in Receive Band <sup>(2)</sup>                          |            | -136.5<br>-142 | -135<br>-138 | dBm/Hz |                                                                            | m, V <sub>MODE1</sub> = 0 V, V<br>, V <sub>MODE1</sub> = +2.4 V |

| Harmonics<br>2fo<br>3fo, 4fo                                  |            | -38<br>-46     | -30<br>-35   | dBc    |                                                                            |                                                                 |

| Input Impedance                                               | -          | -              | 2:1          | VSWR   |                                                                            |                                                                 |

| Spurious Output Level (all spurious outputs)                  | -          | -              | -70          | dBc    | See note 3                                                                 |                                                                 |

| Load mismatch stress with no permanent degradation or failure | 8:1        | -              | -            | VSWR   | Applies over full                                                          | operating range                                                 |

## Notes:

<sup>(1)</sup> ACLR and Efficiency measured at 1950 MHz.

<sup>(2) 2110</sup> MHz to 2170 MHz.

<sup>(3)</sup> Pout < +28.5 dBm, In-band load VSWR < 5:1, Out-of-band load VSWR < 10:1. Applies over all operating conditions.

## APPLICATION INFORMATION

Application Notes on the ANADIGICS web site: http://www.anadigics.com

## **Shutdown Mode**

The power amplifier may be placed in a shutdown mode by applying logic low levels (see Operating Ranges table) to the VENABLE and VMODE1 pins.

## **Bias Modes**

The power amplifier may be placed in either a Low Bias mode or a High Bias mode by applying the appropriate logic level (see Operating Ranges table) to VMODE1.

The Bias Control table lists the recommended modes of operation for various applications. VMODE2 is not necessary for this PA.

Two operating modes are available to optimize current consumption. High Bias/High Power operating mode is for Pout levels > 16 dBm. At around 16 dBm output power, the PA should be "Mode Switched" to Low power mode for lowest quiescent current consumption.

**Table 6: Bias Control**

| APPLICATION          | Pout<br>LEVELS      | BIAS<br>MODE | VENABLE | V <sub>MODE1</sub> | Vcc         | <b>V</b> BATT |

|----------------------|---------------------|--------------|---------|--------------------|-------------|---------------|

| UMTS - low power     | <u>&lt;</u> +16 dBm | Low          | +2.4 V  | +2.4 V             | 3.2 - 4.2 V | ≥ 3.2 V       |

| UMTS - high power    | > +16 dBm           | High         | +2.4 V  | 0 V                | 3.2 - 4.2 V | ≥ 3.2 V       |

| OPTIONAL - low power | <u>&lt;</u> +7 dBm  | Low          | +2.4 V  | +2.4 V             | 1.5 - 3.2 V | ≥ 3.2 V       |

| Shutdown             | -                   | Shutdown     | 0 V     | 0 V                | 3.2 - 4.2 V | ≥ 3.2 V       |

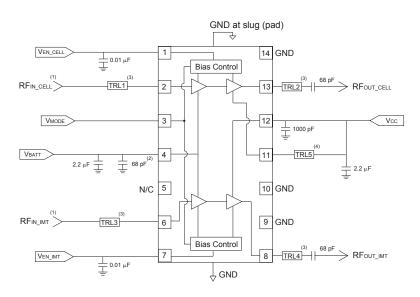

#### Note:

(1) Add blocking cap if DC voltage is present on input pin.

Optional 4.7 nH Inductor may be substituted.

- (2) 68 pF cap should be placed as close as possible to Pin 4.

- (3) TRL should be short and of 50  $\Omega$  characteristic impedance. (4) TRL 5 should be as long as possible (minimum of 0.1  $\lambda$  at 800 MHz) and capable of handling 750 mA current.

Figure 3: Application Circuit

www.DataSheet4U.com

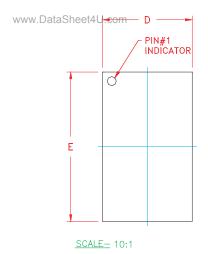

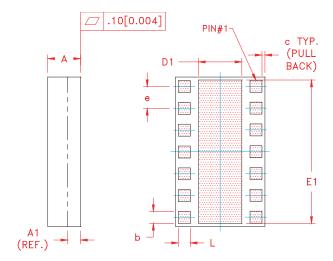

## **PACKAGE OUTLINE**

| S <sub>YMBOL</sub> | MILLIMETERS |         |      |       | NOTE         |       |   |  |

|--------------------|-------------|---------|------|-------|--------------|-------|---|--|

| -oL                | MIN.        | NOM.    | MAX. | MIN.  | NOM.         | MAX.  |   |  |

| Α                  | 0.90        | 1.00    | 1.10 | 0.035 | 0.039        | 0.043 | - |  |

| A1                 | 0.          | 35 (REF | )    | 0.0   | 0.014 (REF.) |       |   |  |

| b                  | 0.37        | -       | 0.57 | 0.015 | -            | 0.022 | 3 |  |

| С                  | -           | 0.10    | _    | _     | 0.004        | -     | _ |  |

| D                  | 2.88        | 3.00    | 3.12 | 0.113 | 0.118        | 0.123 | - |  |

| D1                 | 1.58        | -       | 1.83 | 0.062 | -            | 0.072 | 3 |  |

| Е                  | 4.88        | 5.00    | 5.12 | 0.192 | 0.197        | 0.202 | _ |  |

| E1                 | 4.75        | -       | 4.85 | 0.187 | -            | 0.190 | 3 |  |

| e                  | -           | ∷0.73∷  | -    | -     | :0.029       | -     | 4 |  |

| L                  | 0.33        | _       | 0.52 | 0.013 | _            | 0.020 | 3 |  |

#### NOTES:

- 1. CONTROLLING DIMENSIONS: MILLIMETERS

- 1. CONTROLLING DIMENSIONS: MILLIMETERS

2. UNLESS SPECIFIED TOLERANCE=±0.076[0.003].

3. PADS (INCLUDING CENTER) SHOWN UNIFORM SIZE FOR REFERENCE ONLY.

ACTUAL PAD SIZE AND LOCATION WILL VARY WITHIN MIN. AND MAX. DIMENSIONS ACCORDING TO SPECIFIC LAMINATE DESIGN.

- 4. PITCH MEASUREMENT (e) TAKEN CENTERLINE TO CENTERLINE OF SOLDER MASK OPENINGS. 5. UNLESS SPECIFIED DIMENSIONS ARE SYMMETRICAL ABOUT CENTER LINES SHOWN.

BRANDING SPECIFICATION

Figure 4: Package Outline - 14 Pin 3 mm x 5 mm x 1 mm Surface Mount Module

## TOP BRAND

#### NOTES:

1. PIN 1 INDICATOR:

LASER MARK

2. ANADIGICS LOGO SIZE: NONE

TYPE: ARIAL 3. TEXT : SIZE: AS LARGE AS POSSIBLE

4. PART # 6222R = RoHS COMPLIANT

5. YEAR AND WORK WEEK: YYWW: YY = YEAR, WW = WORK WEEK

6. WAFER LOT NUMBER: LLLL = WAFER LOT#. WAFER ID: NN = WAFER ID:

7. BOM NUMBER: 096

8. COUNTRY CODE: CC = TH -for- THAILAND, TW -for- TAIWAN, PH -for- PHILLIPPINES, CH -for- CHINA, ID -for- INDONESIA, HK -for- HONG KONG

Figure 5: Branding Specification

www.DataSheet4U.com

## **AWT6222**

## ORDERING INFORMATION

| W | ww.DataSheet4U.com<br>ORDER<br>NUMBER | TEMPERATURE<br>RANGE | PACKAGE<br>DESCRIPTION                                              | COMPONENT PACKAGING                 |

|---|---------------------------------------|----------------------|---------------------------------------------------------------------|-------------------------------------|

|   | AWT6222RM28Q7                         | -30 °C to +85 °C     | RoHS Compliant 14 Pin<br>3 mm x 5 mm x 1 mm<br>Surface Mount Module | Tape and Reel, 2500 pieces per Reel |

|   | AWT6222RM28P9                         | -30 °C to +85 °C     | RoHS Compliant 14 Pin<br>3 mm x 5 mm x 1 mm<br>Surface Mount Module | Partial Tape and Reel               |

## ANADIGICS, Inc.

141 Mount Bethel Road Warren, New Jersey 07059, U.S.A.

Tel: +1 (908) 668-5000 Fax: +1 (908) 668-5132

URL: http://www.anadigics.com E-mail: Mktg@anadigics.com

## **IMPORTANT NOTICE**

ANADIGICS, Inc. reserves the right to make changes to its products or to discontinue any product at any time without notice. The product specifications contained in Advanced Product Information sheets and Preliminary Data Sheets are subject to change prior to a product's formal introduction. Information in Data Sheets have been carefully checked and are assumed to be reliable; however, ANADIGICS assumes no responsibilities for inaccuracies. ANADIGICS strongly urges customers to verify that the information they are using is current before placing orders.

#### WARNING

ANADIGICS products are not intended for use in life support appliances, devices or systems. Use of an ANADIGICS product in any such application without written consent is prohibited.

www.DataSheet4U.com