#### Features

- Dual PWM Controller

- Ultra low start-up current, less than 25µA

- Main converter soft-start

- Frequency randomizer for improved EMI performance

- Bulk detect circuitry

- Remote ON/OFF control

- Buffered ramp for slope compensation

- Optional auxiliary converter primary regulation

- High main converter drive capability

- Undervoltage lockout circuitry

- Accurate reference

- Standard temperature range extended to 105°C

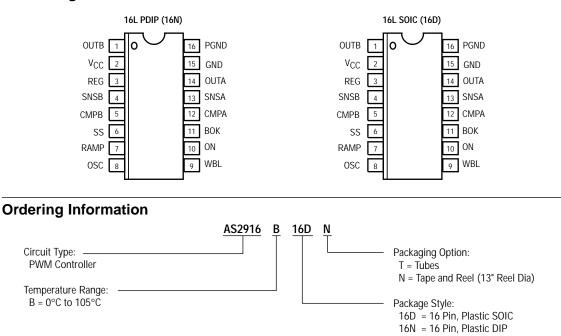

#### Pin Configuration - Top View

#### Description

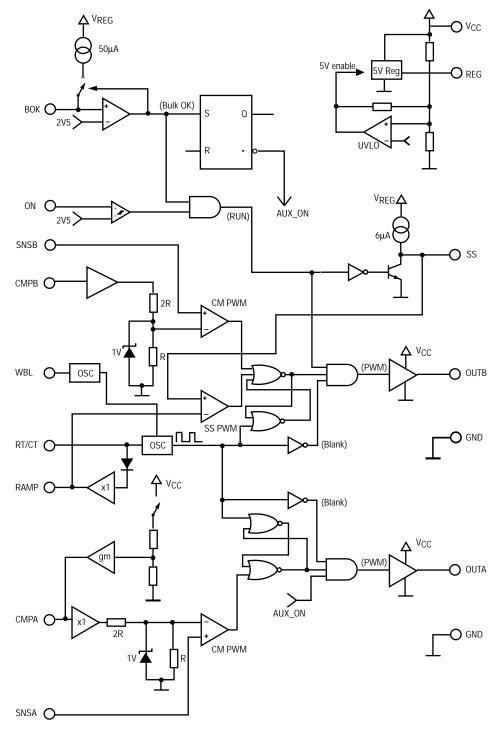

The AS2916 is a dual, full featured, pulse width modulation controller. The second controller is intended to run the auxiliary supply. Both controllers share common oscillator and power up logic. Based on an improved AS3842, the AS2916 provides additional features that reduce component count and improve specifications in a wide range of power supply designs. The added functionality also includes bulk voltage sensing, overvoltage input and soft-start.

The PWM function is controlled by the current sense comparator for normal current mode control and a second comparator for voltage mode soft-start. A buffered RAMP signal is available for slope compensation without loading the oscillator. The output stage is a high current totem pole output that sees only 140 ns delay from the PWM comparators.

The AS2916 requires less than 25  $\mu$ A of startup current. The undervoltage lockout (UVLO) thresholds are nominally 13.5 V for turn-on and 7.5 V for turn-off. The oscillator discharge current is trimmed to provide guaranteed duty cycle clamping. The AS2916 has a second low frequency oscillator, which frequency modulates the operating frequency of the PWM by 25%, thus reducing EMI emissions.

# www.DataSheet.in

#### **Functional Block Diagram**

# **Pin Function Description**

| Pin Number | Function        | Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | OUTB            | This is the gate drive output for the Main FET. The totem pole<br>output has equivalent of an extra 10 $\Omega$ resistor to limit the FET<br>turn on speed and a pull down resistor to ensure the FET gate<br>is never open. No external circuitry except for the FET is<br>expected on this pin. The largest FET expected to be driven is<br>IRFBC40. If a larger power FET is used, a buffer might be<br>required. |

| 2          | V <sub>CC</sub> | Positive supply for the IC. Absolute maximum rating is 20 V.<br>The running voltage shall be provided by the Auxiliary conver<br>tor.                                                                                                                                                                                                                                                                                |

| 3          | REG             | Output of 5 V series regulator.                                                                                                                                                                                                                                                                                                                                                                                      |

| 4          | SNSB            | This is the Main convertor current sense pin. An external RC filter from the Main power FET and slope compensation resistor from the RAMP pin is all the expected external circuitry.                                                                                                                                                                                                                                |

| 5          | СМРВ            | This is the Main output control pin. An opto isolated control signal from the secondary side error amplifier is buffered and connected to the invert pin of the main output current mode comparator. A pull-up current of 1 mA is provided so the only external circuitry expected is a common emitter opto-isolator.                                                                                                |

| 6          | SS              | This pin provides a 6 $\mu$ A current source to linearly charge an external capacitor. This spin is compared to the RAMP pin in the soft start comparator, terminating output pulses when RAMP goes above the SS voltage. While this pin is held low, the main output is inhibited.                                                                                                                                  |

| 7          | RAMP            | This pin is a level-shifted and buffered oscillator waveform,<br>used to provide slope compensation for the Main and Auxiliary<br>converters. The pin also serves as the non-inverting input of<br>the soft-start comparator.                                                                                                                                                                                        |

| 8          | OSC             | Oscillator frequency and maximum duty cycle are set by connecting the resistor ( $R_T$ ) to $V_{REG}$ and a capacitor ( $C_T$ ) to ground.                                                                                                                                                                                                                                                                           |

| 9          | WBL             | Provides an FM modulation of the oscillator, approximately<br>±25% deviation frequency, at a modulation rate set by an exter-<br>nal cap at WBL. Shorting to GND eliminates modulation.                                                                                                                                                                                                                              |

| 10         | ON              | This pin is used to remotely turn the main convertor ON/OFF either for normal user application or for protection.                                                                                                                                                                                                                                                                                                    |

| 11         | ВОК             | Bulk OK. This is a brownout protection feature. The pin moni-<br>tors the bulk voltage through a resistor divider. When BOK<br>exceeds 2.5 V a 50 $\mu$ A current is sourced from the pin for hys-<br>teresis. When the pin drops below 2.5 V the hysteresis is<br>turned off and SS is pulled low,inhibiting the main output.                                                                                       |

|            |                 | The Auxiliary output is not tied to BOK and will run as long as there is sufficient bias voltage.                                                                                                                                                                                                                                                                                                                    |

## **Pin Function Description**

| Pin Number | Function | Description                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 12         | CMPA     | This is the Auxiliary convertor error amplifier compensation pin<br>or if secondary controller is desired, the Auxiliary control input<br>pin. A simple capacitor to ground is the only circuitry expected.                                                                                                                                                                                                              |  |  |  |

| is         |          | Note: There is no external connection for voltage feedback. Voltage sensing is provided internally in such a way that $V_{CC}$ not loaded until it reaches predefined threshold. If secondary control is required, it can be forced into the CMPA pin.                                                                                                                                                                   |  |  |  |

| 13         | SNSA     | This is the Auxiliary convertor current sense pin. An external RC filter from the Auxiliary power FET and slope compensation resistor from the RAMP pin is all the expected external circuitry.                                                                                                                                                                                                                          |  |  |  |

| 14         | OUTA     | This is the gate drive output for the Auxiliary FET. The totem<br>pole output has equivalent of an extra 33 $\Omega$ resistor to limit the<br>FET turn on speed and a pull down resistor to ensure the FET<br>gate is never open. No external circuitry except for the FET is<br>expected on this pin. The largest FET expected to be driven is<br>IRF820. If a larger power FET is used, a buffer might be<br>required. |  |  |  |

| 15         | GND      | Signal ground.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 16         | PGND     | Power ground.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

## **Absolute Maximum Ratings**

| Parameter                                | Symbol           | Rating      | Unit |

|------------------------------------------|------------------|-------------|------|

| Reference Current                        | I <sub>REF</sub> | 200         | mA   |

| Output Current                           | IOUT             | 1           | A    |

| Supply Voltage                           | V <sub>CC</sub>  | 20          | V    |

| Output Voltage                           | V <sub>OUT</sub> | 20          | V    |

| Continuous Power                         | PD               | 500         | mW   |

| Junction Temperature                     | Тј               | 150         | °C   |

| Storage Temperature                      | T <sub>STG</sub> | -60 to +150 | °C   |

| Lead Temperature (Soldering, 10 seconds) | т                | 300         | °C   |

## **Electrical Characteristics**

Electrical characteristics are guaranteed over the full junction temperature range (0-105°). Ambient temperature must be derated based upon power dissipation and package thermal characteristics. The conditions are:  $V_{CC}$  = 15 V, BOK = 3 V, ON = 3 V, R<sub>T</sub> = 680  $\Omega$ , C<sub>T</sub> = 10 nF, and C<sub>WBL</sub> = 2.2 nF, unless otherwise specified. To override UVLO, V<sub>CC</sub> should be raised above UVLO<sub>HIGH</sub> prior to test.

| Parameter                 | Symbol             | Test Condition                                                            | Min. | Тур. | Max. | Unit  |

|---------------------------|--------------------|---------------------------------------------------------------------------|------|------|------|-------|

| 5 V Regulator             |                    |                                                                           | -    | •    | •    | •     |

| Output Voltage            | V <sub>REG</sub>   | T <sub>J</sub> = 25°C, I <sub>REG</sub> = 1 mA                            | 4.90 | 5.00 | 5.10 | V     |

| Line Regulation           | PSRR               | $12 \le V_{CC} \le 18 V$                                                  |      | 5    | 15   | mV    |

| Load Regulation           |                    | $1.0 \le I_{REG} \le 20 \text{ mA}$                                       |      | 5    | 15   | mV    |

| Temperature Stability     | TCREG              |                                                                           |      | 0.2  | 0.4  | mV/°C |

| Total Output Variation    |                    | Line, Load, Temperature                                                   | 4.85 |      | 5.15 | V     |

| Long-Term Stability       |                    | Over 1,000 hrs at 25°C                                                    |      | 5.0  | 25   | mV    |

| Output Noise Voltage      | V <sub>NOISE</sub> | $10 \le f \le 100 \text{ kHz}, \text{ T}_{\text{J}} = 25^{\circ}\text{C}$ |      | 50   |      | μV    |

| Maximum Source Current    | IMAX               | VREG = 4.8 V                                                              | 30   | 120  | 180  | mA    |

| Oscillator                |                    |                                                                           |      |      | -    |       |

| Initial Frequency         | fosc               | T <sub>A</sub> = 25°C, V <sub>WBL</sub> = 0 V                             | 117  | 132  | 143  | kHz   |

| Voltage Stability         |                    | $8.5 \text{ V} \le \text{V}_{CC} \le 18 \text{V}$                         |      | 0.2  | 1.0  | %     |

| Temperature Stability     | тс <sub>ғ</sub>    | $T_{MIN} \le T_J \le T_{MAX}$                                             |      | 5    |      | %     |

| Amplitude                 | Vosc               | V <sub>OSC</sub> peak-to-peak                                             |      | 1.55 |      | V     |

| Upper Trip Point          | VH                 | V <sub>WBL</sub> = 0 V                                                    |      | 2.8  |      | V     |

| Lower Trip Point          | VL                 | V <sub>WBL</sub> = 0 V                                                    |      | 1.25 |      | V     |

| Discharge Current         | IDSC               | V <sub>OSC</sub> = 3 V                                                    | 7.5  | 8.7  | 9.5  | mA    |

| Duty Cycle Limit          |                    | $R_T = 680 \Omega$ , $C_T = 10 nF$ ,<br>$T_J = 25$ °C                     | 46   | 50   | 54   | %     |

| Over-Temperature Shutdown | TOT                |                                                                           |      | 140  |      | °C    |

| Wobble Oscillator         |                    |                                                                           |      |      |      |       |

| Wobble Rate               | F <sub>WBL</sub>   | 2.2 nF WBL to GND                                                         | 3.4  | 4.5  | 6.0  | kHz   |

| OSC Frequency Deviation   | DEV                | Change in main oscillator freq.                                           | +30  | +40  | +50  | kHz   |

| Amplitude                 | V <sub>WBL</sub>   | V <sub>WBL</sub> peak-to-peak                                             |      | 1.8  |      | V     |

| Upper Trip Point          | ٧ <sub>H</sub>     |                                                                           |      | 2.7  |      | V     |

| Lower Trip Point          | VL                 |                                                                           |      | 0.9  |      | V     |

| Charge Current            | ICHRG              | V <sub>WBL</sub> = 0.7 V                                                  | -25  | -36  | -50  | μA    |

| Discharge Current         | IDSC               | V <sub>WBL</sub> = 4.8 V                                                  | 25   | 36   | 50   | μA    |

#### **Electrical Characteristics**

Electrical characteristics are guaranteed over the full junction temperature range (0-105°). Ambient temperature must be derated based upon power dissipation and package thermal characteristics. The conditions are:  $V_{CC}$  = 15 V, BOK = 3 V, ON = 3 V, R<sub>T</sub> = 680  $\Omega$ , C<sub>T</sub> = 10 nF, and C<sub>WBL</sub> = 2.2 nF, unless otherwise specified. To override UVLO, V<sub>CC</sub> should be raised above UVLO<sub>HIGH</sub> prior to test.

| Parameter                      | Symbol              | Test Condition                                                                            | Min. | Тур. | Max. | Unit  |

|--------------------------------|---------------------|-------------------------------------------------------------------------------------------|------|------|------|-------|

| Auxiliary PWM Comparator Input | (CMPA)              |                                                                                           | •    | •    |      |       |

| Regulation Voltage             | VCCREG              |                                                                                           | 13.4 | 14.5 | 15.7 | V     |

| Transconductance               | G <sub>m</sub>      |                                                                                           |      | 1.0  |      | mS    |

| Output Sink Current            | ICMPALow            | V <sub>CC</sub> = 16 V, V <sub>CMPA</sub> = 1.1 V                                         | 2.0  | 6.0  |      | mA    |

| Output Source Current          | ICMPAHigh           | V <sub>CC</sub> = 12 V, V <sub>CMPA</sub> = 5 V                                           | -0.5 | -1.1 |      | mA    |

| Output Swing High              | VCMPAHig            | h V <sub>CC</sub> = 12 V, I <sub>CMPA</sub> = 0.5 mA                                      | 5.4  | 5.7  |      | V     |

| Output Swing Low               | VCMPALow            | , V <sub>CC</sub> = 16 V, I <sub>CMPA</sub> = 2 mA                                        |      | 0.2  | 1.1  | V     |

| Auxiliary Current Sense Com    | parator (SN         | SA)                                                                                       |      |      |      | ·     |

| Transfer Gain                  | A <sub>VSNSA</sub>  | $-0.2 \le V_{SNSA} \le 0.8 \text{ V}$                                                     |      | 3.0  |      | V/V   |

| CMPA Level Shift               | V <sub>LS</sub>     | V <sub>SNSA</sub> = 0 V                                                                   |      | 1.5  |      | V     |

| Current Sense Threshold        | V <sub>SNSA</sub>   | V <sub>CMPA</sub> = 5 V                                                                   | 0.95 | 1.05 | 1.15 | V     |

| Input Bias Current             | IBIAS               |                                                                                           |      | -1.0 | -10  | μA    |

| Propagation Delay to Output    | <sup>t</sup> PD     |                                                                                           |      | 80   | 150  | ns    |

| Main PWM Comparator Input      | (CMPB)              |                                                                                           |      |      |      |       |

| Comp Source Current            | ІСМРВ               | V <sub>CMPB</sub> = 2.5 V                                                                 | -1.0 | -1.4 |      | mA    |

| Comp Source Impedance          | Z <sub>CMPB</sub>   |                                                                                           | 10   | 15   | 20   | kΩ    |

| Comp Source High               | VCMPBHig            | h                                                                                         | 5.4  | 5.6  |      | V     |

| Main Current Sense Compara     | tor (SNSB)          |                                                                                           |      |      |      |       |

| Transfer Gain                  | A <sub>VSNSB</sub>  | $-0.2 \leq V_{\mbox{SNSB}} \leq 0.8 \ \mbox{V}$                                           |      | 3.0  |      | V/V   |

| CMPB Level Shift               | V <sub>LS</sub>     | V <sub>SNSB</sub> = 0 V                                                                   |      | 1.5  |      | V     |

| Current Sense Threshold        | V <sub>SNSB</sub>   | V <sub>CMPB</sub> = 5 V                                                                   | 0.95 | 1.05 | 1.15 | V     |

| Input Bias Current             | IBIAS               |                                                                                           |      | -1.0 | -10  | μA    |

| Propagation Delay to Output    | <sup>t</sup> PD     |                                                                                           |      | 80   | 150  | ns    |

| Soft Start Comparator          |                     |                                                                                           |      |      |      |       |

| SS Charge Current              | ICharge SS          | V <sub>SS</sub> ≤ V <sub>RAMP</sub>                                                       | -4.0 | -6.0 | -10  | μA    |

| SS Discharge Current           | IDsc SS             | V <sub>SS</sub> = 1 V, V <sub>ON</sub> <1.5 V                                             | 2.0  | 10   |      | mA    |

| SS Lower Clamp                 | V <sub>SS low</sub> |                                                                                           |      | 0.05 | 0.2  | V     |

| Propagation Delay to Output    | t <sub>PB</sub>     |                                                                                           |      | 50   | 100  | ns    |

| RAMP High Level                | VRAMPH              | T <sub>J</sub> = 25°C                                                                     | 2.0  | 2.15 | 2.3  | V     |

| RAMP Low Level                 | VRAMPL              | T <sub>J</sub> = 25°C                                                                     | 0.45 | 0.6  | 0.75 | V     |

| RAMP Levels T <sub>C</sub>     |                     | Note: RAMP waveform is same<br>as OSC waveform, but level<br>shifted down one diode drop. |      | -2.0 |      | mV/°C |

| RAMP Sink Current              | IRAMPL              | T <sub>J</sub> = 25°C                                                                     | 0.1  | 0.2  |      | mA    |

| RAMP Source Current            | IRAMPH              | T <sub>J</sub> = 25°C                                                                     | -2.0 | -10  |      | mA    |

## **Electrical Characteristics**

Electrical characteristics are guaranteed over the full junction temperature range (0-105°). Ambient temperature must be derated based upon power dissipation and package thermal characteristics. The conditions are:  $V_{CC}$  = 15 V, BOK = 3 V, ON = 3 V, R<sub>T</sub> = 680  $\Omega$ , C<sub>T</sub> = 10 nF, and C<sub>WBL</sub> = 2.2 nF ,unless otherwise specified. To override UVLO, V<sub>CC</sub> should be raised above UVLO<sub>HIGH</sub> prior to test.

| Parameter                             | Symbol               | Test Condition                                                                  | Min. | Тур.  | Max.  | Unit |

|---------------------------------------|----------------------|---------------------------------------------------------------------------------|------|-------|-------|------|

| Main Output                           | · .                  |                                                                                 |      |       | 1     |      |

| Output Low Level                      | VOUTBL               | I <sub>SINK</sub> = 10 mA                                                       |      | 0.1   | 0.4   | V    |

| Output Low Level                      | VOUTBL               | I <sub>SINK</sub> = 150 mA                                                      |      | 1.5   | 2.2   | V    |

| Output High Level                     | VOUTBH               | I <sub>SOURCE</sub> = 10 mA, V <sub>CC</sub> = 15 V                             | 12   | 13    |       | V    |

| Output High Level                     | VOUTBH               | I <sub>SOURCE</sub> = 150 mA, V <sub>CC</sub> = 15V                             | 10   | 10.7  |       | V    |

| On Resistance High                    |                      |                                                                                 |      | 10    |       | Ω    |

| Rise Time                             | <sup>t</sup> R       | C <sub>L</sub> = 1.3 nF, 10% to 90%                                             |      | 50    | 150   | ns   |

| Fall Time                             | t <sub>F</sub>       | C <sub>L</sub> = 1.3 nF, 90% to 10%                                             |      | 50    | 150   | ns   |

| Output Impedance to GND in UVLO State | Z <sub>OUT</sub>     | VCC = 6 V                                                                       |      | 20    |       | kΩ   |

| Auxiliary Output                      | · · · ·              |                                                                                 |      |       |       |      |

| Output Low Level                      | VOUTBL               | I <sub>SINK</sub> = 10 mA                                                       |      | 0.1   | 0.4   | V    |

| Output Low Level                      | VOUTBL               | I <sub>SINK</sub> = 150 mA                                                      |      | 1.5   | 2.2   | V    |

| Output High Level                     | VOUTBH               | ISOURCE = 10 mA, V <sub>CC</sub> = 15V,<br>V <sub>CMPA</sub> = 5 V              | 12   | 13    |       | V    |

| Output High Level                     | VOUTBH               | I <sub>SOURCE</sub> = 110 mA, V <sub>CC</sub> = 15V,<br>V <sub>CMPA</sub> = 5 V | 7    | 8     |       | V    |

| On Resistance High                    |                      |                                                                                 |      | 33    |       | Ω    |

| Rise Time                             | <sup>t</sup> R       | C <sub>L</sub> =350 pF, 10% to 90%                                              |      | 70    | 150   | ns   |

| Fall Time                             | t <sub>F</sub>       | C <sub>L</sub> = 350 pF, 90% to 10%                                             |      | 50    | 150   | ns   |

| Output Impedance to GND in UVLO State | Z <sub>OUT</sub>     | V <sub>CC</sub> = 6 V                                                           |      | 20    |       | kΩ   |

| Under-Voltage Lockout                 | · · ·                | ·                                                                               |      |       |       |      |

| Start-Up Threshold                    | V <sub>CC(ON)</sub>  |                                                                                 | 12.4 | 13.5  | 14.7  | V    |

| Stop Threshold                        | V <sub>CC(OFF)</sub> |                                                                                 | 7    | 7.5   | 8     | V    |

| Start-Up Current                      | ICC                  |                                                                                 |      | 0.1   | 25    | μA   |

| Operating Supply Current              | ICC                  | V <sub>CC</sub> = 15 V                                                          |      | 18    | 25    | mA   |

| Housekeeping                          |                      |                                                                                 |      | 1     |       |      |

| BOK UV Threshold                      | VBOK UV              | T <sub>J</sub> = 25°C                                                           | 2.50 | 2.537 | 2.575 | V    |

| BOK UV Hysteresis Current             |                      | V <sub>BOK</sub> = 2.6 V                                                        | 42   | 50    | 58    | μA   |

| BOK Input Bias Current                | IBOK                 | V <sub>BOK</sub> = 2.4 V                                                        |      | -0.1  | -1.0  | μA   |

| ON Threshold                          | VON                  |                                                                                 | 2.35 | 2.5   | 2.65  | V    |

| ON Hysteresis                         | $\Delta V_{ON}$      |                                                                                 | -0.7 | -0.9  | -1.1  | V    |

| ON Bias Current                       | IBIAS ON             | V <sub>ON</sub> = 2.3 V                                                         |      | -0.5  | -10   | μA   |